- 1. 3次元TCADシステム Advance/TCAD

- 1.1. LSI デバイス設計 CAD システム

- 1.2. Advance/TCADの概要

- 1.3. システム構成

- 1.4. 統合プラットフォーム

- 1.5. 機能一覧

- 1.5.1. プロセスシミュレータ機能一覧

- 1.6. デバイスシミュレータ機能一覧

- 1.7. 解析事例

- 1.7.1. 解析事例 1 | イオン注入計算事例

- 1.7.2. 解析事例 2 | 幾何学的処理による高速3次元構造生成事例

- 1.7.3. 解析事例 3 | 5段CMOSインバータチェイン

- 1.7.4. 解析事例 4 | モータ制御デバイス解析

- 1.7.5. 解析事例 5 | 大規模デバイス計算並列化効率検証事例

- 1.7.6. 解析事例 6 | SRAMソフトエラーのデバイスシミュレーション

- 1.7.6.1. SRAMソフトエラーの原理

- 1.7.6.2. デバイスシミュレーションの解析モデル

- 1.7.6.3. デバイスシミュレーション解析条件

- 1.7.7. 計算結果

- 1.8. Advance/TCAD を用いた研究発表

- 1.9. Advance/TCADについて

- 1.10. 関連記事一覧

3次元TCADシステム Advance/TCAD

LSI デバイス設計 CAD システム

超微細半導体デバイスからパワーデバイスまでの解析において、複数デバイスの一体解析(セルレベルシミュレーション)やデバイス・外部回路(LCR)一体解析(Advanced mixed-modes)等の高度な機能と使いやすいGUIを備えた、お客さまのご要望に臨機応変に対応できる国産の3次元TCADシステムを提供します。

- 高速3次元解析

- 頑健(ロバスト)な計算手法

- 幅広いデバイスに対応

- 大規模解析

Advance/TCADの概要

独自に開発した高速で安定的な計算手法や分散メモリ型並列計算機能の採用などにより高速でロバストな大規模3次元プロセス・デバイス計算が可能です。 各種の物性値や計算パラメータはユーザにより任意の値が設定可能です。研究から製造までの幅広い用途にご使用いただけます。 超微細デバイス、パワーデバイスのそれぞれの解析に特有な解析機能を備えています。

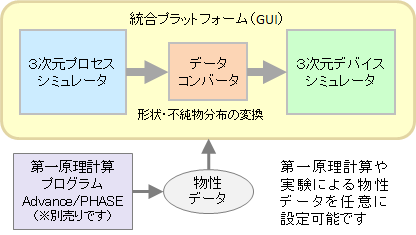

システム構成

- プロセスシミュレータは、メッシュ生成、形状生成、イオン注入、酸化、拡散の3次元解析機能を搭載しています。対象材料はSiとSiCです。

- デバイスシミュレータは、3次元デバイスの直流・過渡特性を、高速、高精度、ロバストに計算します。大規模計算にも対応しています。対象材料はシリコンの他、化合物系にも対応しています。

- プロセスシミュレーションから得られた形状、不純物分布は異なるメッシュ系のデバイスシミュレーションへデータ変換(コンバータ)されます。

- システム全体を使いやすいGUIで制御しています。

統合プラットフォーム

- プロセス、デバイスの両ソルバの入力設定、起動、終了、出力データのレビューを一つのユーザフレンドリなGUIプログラムで制御します。(※起動、終了制御はWindows版ソルバーのみに対応)

- GDSIIレイアウトデータからマスクデータや構造データを生成できます。

機能一覧

プロセスシミュレータ機能一覧

| 項目 | 値 |

| メッシュ作成機能 | ・格子密度制御機能付き非構造四面体メッシャー |

| 3次元形状生成機能 | ・テトラメッシュ使用 ・距離関数を用いた幾何学処理 ・等方デポ・エッチ、異方デポ・エッチ、平坦化デポ・エッチ |

| イオン注入機能 | ・平均自由行程モデル(アモルファス材質) ・原子間相互作用:ZBL ポテンシャル ・原子・電子間相互作用:LSS,、Firsov、VIENNA モデル ・熱振動モデル:Debyeモデルによる熱振動振幅 ・結晶破壊モデル:Kinchin-Peace モデル |

| 拡散機能 | ・非平衡反応拡散モデル ・Fermiモデル |

| 酸化機能 | ・粘弾性モデルによる酸化-変形連成解析機能 |

デバイスシミュレータ機能一覧

| 項目 | 値 |

| 使用可能な材質 | 半導体:Si, poly-Si, Ge, Si0.3Ge0.7, Si0.5Ge0.5, Si0.7Ge0.3, GaAs, AlAs, Ga0.9Al0.1As, Ga0.8Al0.2As, Ga0.7Al0.3As, 3C-SiC, 4H-SiC, 6H-SiC, GaN, GaAl0.2N0.8, GaAl0.5N0.5, GaAl0.8N0.2, AlN 絶縁体:SiO2, Si3N4, Ta2O5, Al2O3, Air 金属:Cu, Al, Ti, Ta, Mo, W, TiN (※材料定数を変更することで別材質も設定可能) |

| 形状生成・メッシュ生成機能 | ・コンバータ出力形状の読み込み機能 ・簡易デバイス形状生成機能 ・Delaunay性を担保した高品質メッシュを使用 ・メッシュの立体粗密調整機能 |

| 解析機能 | ・電子・正孔密度の移流拡散方程式 + ポアソン方程式 ・定常解析、過渡解析機能 ・不純物モデル(浅い準位から深い準位までに対応) ・界面準位モデル(界面再結合, 界面電荷を考慮, 連続準位の設定が可能) ・ヘテロ接合に対応 ・量子効果補正(Feynmanの実効ポテンシャル、直接トンネリング) ・電極特性(オーミック, ショットキー接合に対応) |

| 基本物性のモデル | ・誘電率、電子親和力、質量モデル、バンドギャップモデルなど |

| 移動度モデル | ・MOS反転層モデル、折れ線近似、指数飽和型、定数型など |

| 生成・再結合モデル | ・SRH, Auger、直接再結合、深い準位による再結合、二準位間再結合、GIDL, 衝突電離など |

解析事例

- 解析事例 1 | イオン注入計算事例

- 解析事例 2 | 幾何学的処理による高速3次元構造生成事例

- 解析事例 3 | 5段CMOSインバータチェイン

- 解析事例 4 | モータ制御デバイス解析

- 解析事例 5 | 大規模デバイス計算並列化効率検証事例

- 解析事例 6 | SRAMソフトエラーのデバイスシミュレーション

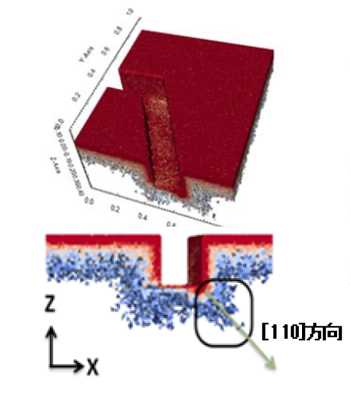

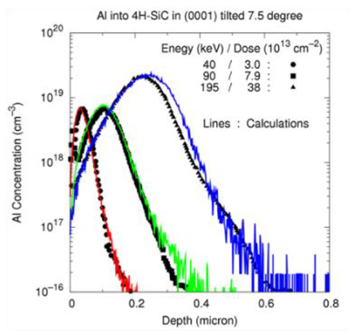

解析事例 1 | イオン注入計算事例

(六角トレンチ構造(Si基板))

(4H-SiC基板へのAl注入)

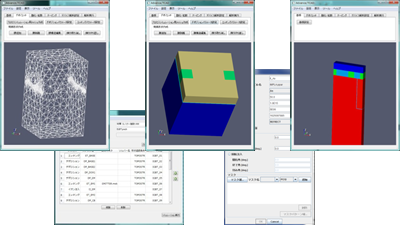

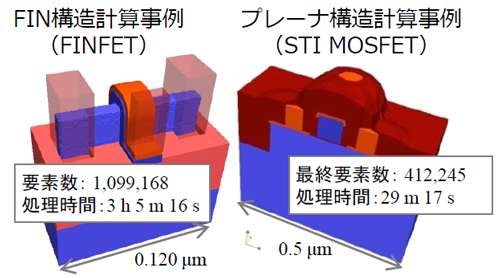

解析事例 2 | 幾何学的処理による高速3次元構造生成事例

- さまざまなデポジション・エッチング工程を幾何学的処理により再現し、3次元形状を高速に生成します。

- 複雑な形状表現にも適した非構造四面体メッシュを使用しています。

- 任意形状のマスクパターンが作成可能です。

- 大規模メッシュも高速で処理できます。

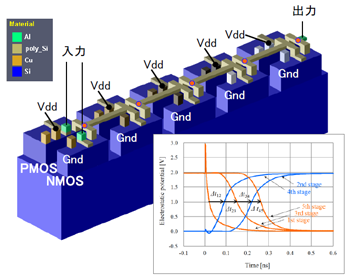

解析事例 3 | 5段CMOSインバータチェイン

複数デバイス+回路モデルの大規模デバイス解析

Advance/TCADではデバイス単体の特性だけでなく回路全体の特性を、3次元デバイスシミュレーションで一括解析することが可能です。これにより従来の回路モデルを中心とした解析と比較して、より高精度な解析が可能となります。

フィードバックをかければリングオシレータとして動作可能

※これらの解析には大規模モデル対応並列計算機能、複数デバイスの一括解析手法、デバイス-回路の一括解析機能を使用しています。

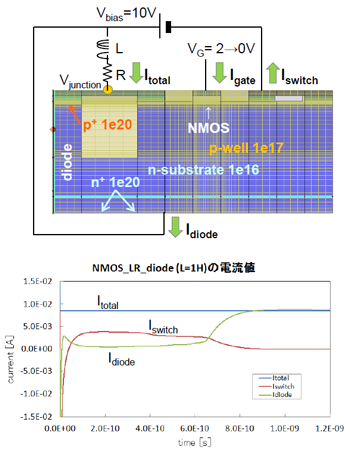

解析事例 4 | モータ制御デバイス解析

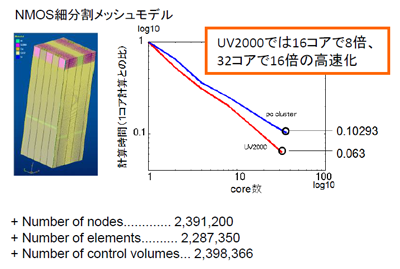

解析事例 5 | 大規模デバイス計算並列化効率検証事例

- 分散メモリ型並列計算機能を搭載しています。

- スーパーコンピュータにも対応しており、計算機資源を最大限に利用した大規模計算が可能です。

解析事例 6 | SRAMソフトエラーのデバイスシミュレーション

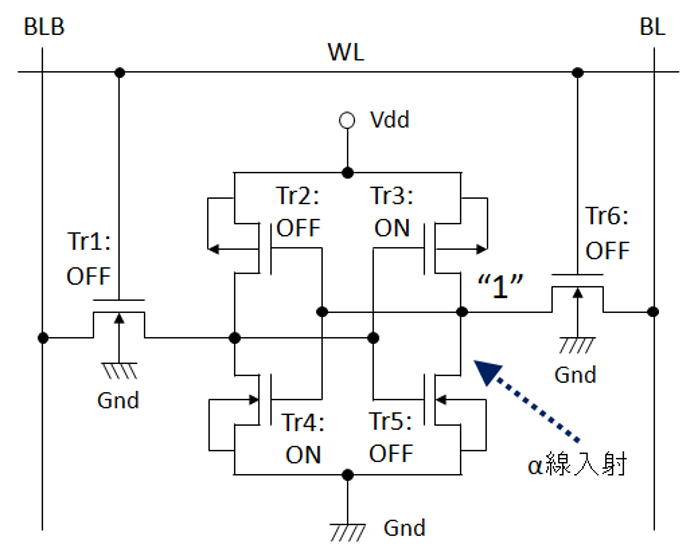

SRAMソフトエラーの原理

- SRAMのインバータ出力部の拡散層付近にα線が入射し、電子・正孔対が発生する。

- pnジャンクション近傍で発生した電子と正孔は、ドリフト・拡散により、それぞれn型とp型領域に移動する。

- インバータの出力部に移動してくる電子や正孔による電位でビットが反転した場合、ソフトエラーとなる。図ではビット“1”から”0”に反転する。

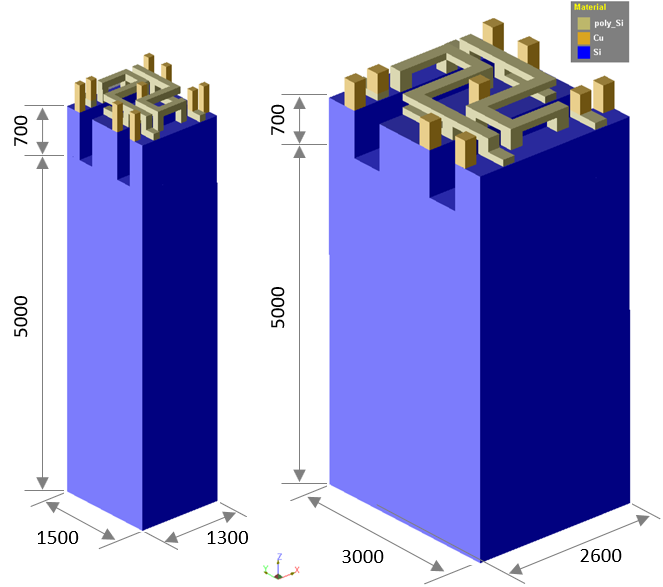

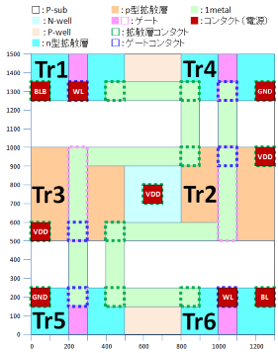

デバイスシミュレーションの解析モデル

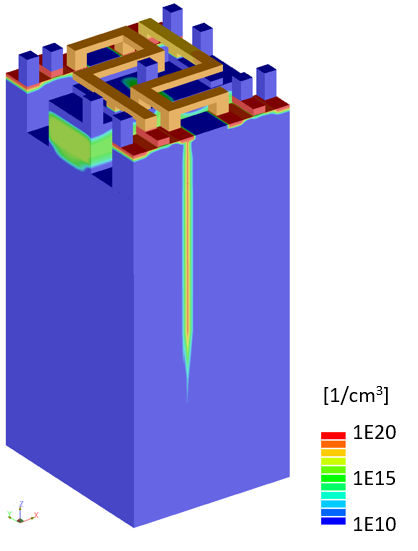

(左:L=100nm、右:L=200nm。手前の角がTr5。SiO2は非表示)

L=200nmモデルは寸法が2倍になる。Tr1~6は図 6-1 の記号に対応している)

- 6個のトランジスタと2本の配線を1つのデバイスシミュレーションモデルとして作成した。

- L=100nmとL=200nmのゲート酸化膜厚は、それぞれ5nmと10nmとした。

- L=100nmのモデルの基板、p-well、n-wellの不純物濃度はL=200nmのモデルの2倍に設定した。

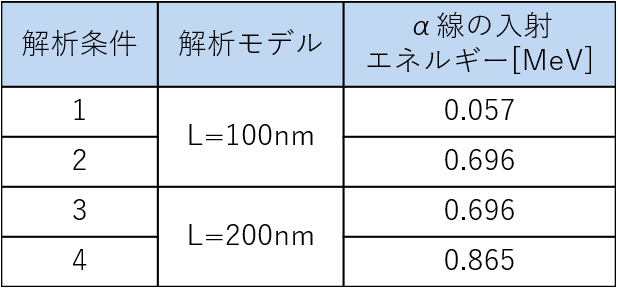

デバイスシミュレーション解析条件

- α線がTr5のドレイン側拡散層に真上から入射したと仮定し、入射エネルギーに応じて電子・正孔対を配置した。

- 一対の電子・正孔対を発生させるのに3.6eVが必要であるとして発生個数を概算した。

- Siの電子的阻止能を2.094×103 (MeV/cm)として、 α線の侵入深さを概算した。

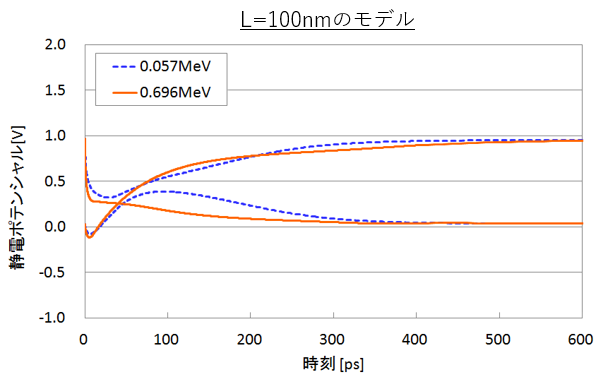

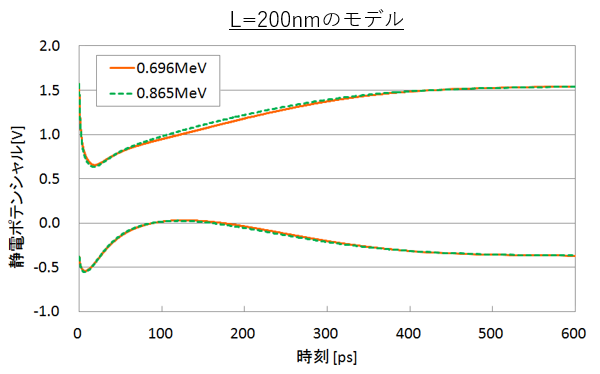

計算結果

図 6-5 α線入射後のインバータ間配線の静電ポテンシャルの時間変化

(無バイアス時を0とした相対値)

- L=100nmでE=0.696MeVの場合にはインバータの出力電位の静電ポテンシャルの大小が逆転し、ソフトエラーとなった。

- それ以外の場合には二つのインバータの出力部の静電ポテンシャルの差は、途中までは小さくなったが逆転するまでには至らず、元のビット“1”の定常状態に戻った。

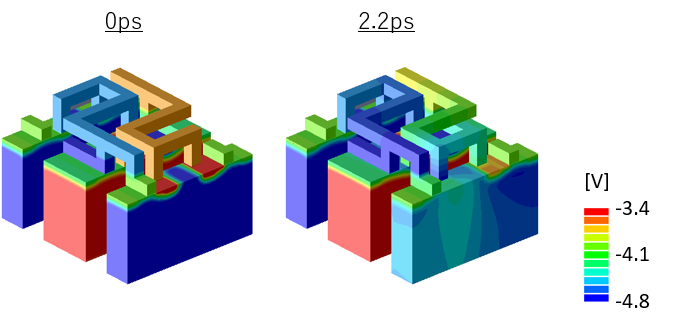

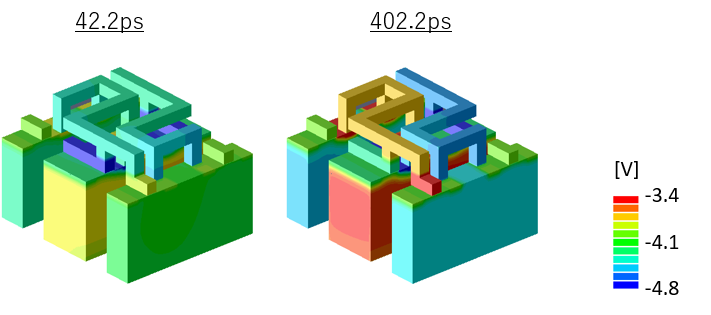

図 6-6 L=100nmでE=0.696MeVの場合(ソフトエラー発生)の

静電ポテンシャル分布の時間変化(SiO2 と電極コンタクトは非表示)

- 時間が進むにつれ、2つの配線およびインバータのゲートの電位の大小が反転していく。

- このように、デバイスシミュレーションで解析したことにより、デバイス全体の静電ポテンシャル分布の時間変化が解析可能となる。

Advance/TCAD を用いた研究発表

- Jun-ichi Matsuda, Anna Kuwana and Haruo Kobayashi, "High Reliability and Low Switching Loss Dual RESURF 40 V N-LDMOS Transistor with Grounded Multi-Step Field Plate", Journal of Technology and Social Science , Vol.7, No.1, pp.1-12, 2023.【フルペーパー】

- Koji Sakui, Nozomu Harada, "Read Non-Destructive Dynamic Flash Memory (DFM) with Dual and Double Gates", 2022 International Conference on Solid State Devices and Materials (SSDM 2022), September 26-29.

- Hao Yang Du, Jun-Ichi Matsuda, Anna Kuwana and Haruo Kobayashi, "Low Switching Loss Dual RESURF 40 V N-LDMOS with Grounded Field Plate for DC-DC Converters", 2022 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS 2022) Converter Circuits & Systems I Session Paper ID 9052, Topic 6.3.[Abstract ]

- Anna Kuwana, Jun-Ichi Matsuda and Haruo Kobayashi, "Analysis of Switching Characteristics of Wide SOA and High Reliability 100 VN-LDMOS Transistor with Dual RESURF and Grounded Field Plate Structure", 2021 IEEE 14th International Conference on ASIC (ASICON).[Abstract ]

- Koji Sakui,Nozomu Harada, "Dynamic Flash Memory with Dual Gate Surrounding Gate Transistor (SGT) for Computation In Memory", 2021 International Conference on Solid State Devices and Materials (SSDM 2021), September 6-9.

- Koji Sakui,Nozomu Harada, "Dynamic Flash Memory with Dual Gate Surrounding Gate Transistor (SGT)", 2021 IEEE International Memory Workshop (IMW).[Abstract ]

- Toshiyuki Tsutsumi, "Dependence of three-dimensional bottleneck barrier height minimum on threshold voltage fluctuated by ion implantation of source and drain extensions in silicon-on-insulator triple-gate fin-type field-effect transistors", 2020 Japanese Journal of Applied Physics 59, SIIE06. [Abstract]

- 松田 順一, 桑名 杏奈, 小林 春夫, "高信頼性、広SOA 100 V N-LDMOSトランジスタの最適化", 電気学会論文誌C(電子・情報・システム部門誌), Vol.140, No.11, pp.1220-1229, 2020.

- Masatoshi Sakai, Weisong Liao, Yugo Okada, and Kazuhiro Kudo, "Carrier-injection and succeeding pre-channel formation in organic thin-film transistor observed with time-domain reflectometry", Journal of Applied Physics 128, 085502 (2020).

- Toshiyuki Tsutsumi, "Three-dimensional exploration of the origin of threshold voltage fluctuation of silicon-on-insulator triple-gate fin-type field-effect transistors caused by ion implantation to source and drain extensions", 2019 Japanese Journal of Applied Physics 58, SDDE06. [Abstract]

- Masatoshi Sakai, Takuto Honda, Kazuhiro Kudo, Yugo Okada, Yuichi Sadamitsu, Yuta Hashimoto, and Nozomi Onodera, "Initial carrier-injection dynamics in organic thin-film transistor observed with time domain reflectometry in thickness direction", Applied Physics Express 12, 051004 (2019).[Abstract ]

- Jun-ichi Matsuda, Jun-ya Kojima, Nobukazu Tsukiji, Masataka Kamiyama and Haruo Kobayashi, "Low Switching Loss and Scalable 20-40 V LDMOS Transistors with Low Specific On-Resistance", Proceedings of 2nd International Conference on Technology and Social Science 2018 Kiryu, Japan, Apr. 18-20, 2018.

- Toshiyuki Tsutsumi, Takeshi Nakamura, Norihiro Yokoyama and Shota Fukuoka, "Accurate analysis of top gate effect of a typical triple-gate fin-type FET using three-dimensional device simulation", Japanese Journal of Applied Physics 55.6S1, 06GG09, 2016. [Abstract ]

- Toshiyuki Tsutsumi, "Very low and broad threshold voltage fluctuation caused by ion implantation to silicon-on-insulator triple-gate fin-type field effect transistor using three-dimensional process and device simulations", Japanese Journal of Applied Physics 56.6S1, 06GF12, 2017. [Abstract ]

- Toshiyuki Tsutsumi, "Origin of threshold voltage fluctuation caused by ion implantation to source and drain extensions of silicon-on-insulator triple-gate fin-type field-effect transistors using three-dimensional process and device simulations", Japanese Journal of Applied Physics 57.6S1, 06HC06, 2018. [Abstract ]

- 村上 裕章, 酒井 正俊, 岡田 悠悟, 山内 博, 貞光 雄一, 橋本 雄太, 工藤 一浩, "ペンタセンTFT構造のタイムドメインリフレクトメトリ ", 第65回応用物理学会春季学術講演会, 20a-D102-6, 2018年3月5日.

- 松田 順一, 小島 潤也, 築地 伸和, 神山 雅貴, 小林 春夫, "低スイッチング損失、広SOAかつ低特性オン抵抗の40 V LDMOSトランジスタ", 電気学会 電子デバイス/半導体電力変換合同研究会, EDD-17-079, SPC-17-178, 2017年11月21日.

- Toshiyuki Tsutsumi, "Study on the Origin of Vth Fluctuation Caused by Ion Implantation to Source and Drain Extensions of SOI Tri-Gate FinFETs by 3D Process and Device Simulations", The 30th International Microprocesses and Nanotechnology Conference (MNC 2017) , 7A-2-5, Nov. 7th, 2017.

- Toshiyuki Tsutsumi and Jaeyup Lee, "Study of threshold voltage fluctuation caused by source and drain extensions doping variation of tri-gate fin-type FET using three-dimensional device simulation", 2014 Japanese Journal of Applied Physics, 53, 06JE06. [Abstract]

Advance/TCADについて

科学技術振興機構 (JST) は平成23年度研究成果最適展開支援プログラム (A-STEP) 本格研究開発ステージ 実用化挑戦タイプにおいてアドバンスソフト株式会社が提案した「半導体デバイス3次元TCADシステム」を採択しました。これに伴い、アドバンスソフト株式会社は本格的なTCADの開発に着手しました。開発期間は平成23年度から平成27年度で、開発担当者はアドバンスソフト株式会社です。このプロジェクトの目的は、世界レベルの本格的「半導体デバイス3次元TCADシステム」を開発し、事業化することです。