# デバイスシミュレーション

山口 憲\* 原田 昌紀\*\*\* 桑原 匠史\*\* 大倉 康幸\*\*

# **Device Simulation**

Ken Yamaguchi\* Masanori Harada\*\* Takuhito Kuwabara\*\* and Yasuyuki Ohkura\*\*

デバイスシミュレーション技術は半導体デバイス開発と並行して発展してきた。1960 年代に発表されたガンダイオードの発振現象解析[1]、バイポーラトランジスターの 1 次元解析[2]にその起源を見ることができる。1970 年代に入ると、Si LSI の幕開けと共に 2 次元デバイス解析技術[3] - [5]が登場、設計現場に浸透してきた。これらの文献はキャリアを連続流体とみなす『流体モデル』と呼ばれるもので、次節で詳述する Boltzamnn 方程式に基付く定式化である。

一方、電場の中の電子の移動を荷電粒子の運動として表現するモンテカルロ法モデリング[6]は電子の運動を詳細に解析できることから物理研究に威力を発揮した。ただし、計算時間を長く必要とするため、実用面からは流体モデルが主流となっている。

本章では、流体モデルに基礎をおくデバイスシミュレーション技術を中心に述べる。Boltzmann 方程式は輸送問題における第一原理式といえるものである。これを基礎にデバイスシミュレーションのための定式化を述べる。

Key word: CMOS、インバータ、一括解析、過渡解析、デバイスシミュレーション、パワーデバイス、ショットキー、バイアス粗密調整、高耐圧計算

# 1. 概要

# 1.1. Boltzmann 方程式

個体中の電子の運動はランダムであり、速度の速いものから遅いものまで幅広い分布をもっている。このような電子の集団を 1 つの分布関数 f で表現することを考える。分布関数 f はある時刻(t)で眺めれば電子の空間位置座標 r(x, y, z)と速度ベクトル  $v(v_x, v_y, v_z)$ の関数で表現され、

$$\frac{\partial f}{\partial t} + \frac{\partial f}{\partial r}\frac{d\mathbf{r}}{dt} + \frac{\partial f}{\partial v}\frac{d\mathbf{v}}{dt} = 0 \tag{1}$$

を得る。上式は時間全微分に対する平衡解を表現したもので、導出に何らの仮定を含まない。分布関数fはいかなる分布関数でもよく、この意味で第一原理式と呼べるものである。次に

\*アドバンスソフト株式会社 総合企画部

General Planning Division, AdvanceSoft Corporation

\*\*アドバンスソフト株式会社 第1事業部

1st Computational Science and Engineering Group,

AdvanceSoft Corporation

$$\frac{d\mathbf{r}}{dt} = \mathbf{v} \tag{2}$$

$$m\frac{d\mathbf{v}}{dt} = \mathbf{F} \tag{3}$$

を考えれば、式(1)は

$$\frac{\partial f}{\partial t} + \mathbf{v} \frac{\partial f}{\partial \mathbf{r}} + \frac{\mathbf{F}}{m} \frac{\partial f}{\partial \mathbf{v}} = 0 \tag{4}$$

と記述される。ここにFは電子に作用する力である。Fを駆動力( $F_e$ )と緩和力( $F_i$ )に分けて考えれば

$$\frac{\partial f}{\partial t} + \mathbf{v} \frac{\partial f}{\partial \mathbf{r}} + \frac{\mathbf{F}_e}{m} \frac{\partial f}{\partial \mathbf{v}} = -\frac{\mathbf{F}_i}{m} \frac{\partial f}{\partial \mathbf{v}} = \left(\frac{\partial f}{\partial t}\right)_{coll} \tag{5}$$

となる。右辺を緩和係数で表現すれば、駆動力に対し、下付き記号( $F_e$ )を用いる必要がなくなり

$$\frac{\partial f}{\partial t} + \mathbf{v} \frac{\partial f}{\partial \mathbf{r}} + \frac{\mathbf{F}}{m} \frac{\partial f}{\partial \mathbf{v}} = \left(\frac{\partial f}{\partial t}\right)_{coll} \tag{6}$$

と表記してよい。上式を Boltzmann 方程式と呼んでいる。

式(6)の両辺に速度空間における任意の物理量 Yを乗算し、速度空間で積分を行うと

$$\int_{-\infty}^{\infty} Y \frac{\partial f}{\partial t} d\mathbf{v} + \int_{-\infty}^{\infty} Y \mathbf{v} \frac{\partial f}{\partial \mathbf{r}} d\mathbf{v} + \int_{-\infty}^{\infty} Y \frac{\mathbf{F}}{m} \frac{\partial f}{\partial \mathbf{v}} d\mathbf{v}$$

$$= \int_{-\infty}^{\infty} Y \left( \frac{\partial f}{\partial t} \right)_{coll} d\mathbf{v} \tag{7}$$

を得る。一方、実空間における物理量が速度空間における物理量 Y に分布関数を重み関数として乗算した統計的平均値

$$\overline{Y(r,t)} = \frac{1}{n(r,t)} \int_{-\infty}^{\infty} Y(r,v,t) f(r,v,t) dv$$

(8)

より求められることを考えると、Y として該当する物理量を充当することで、電子の輸送問題を解くための物理基本式を得ることが可能となる。なお、式(8)の右辺第1項の分母に密度nがあるのは、分布関数が規格化されていないからである。Step 1 物質保存則 (Y=1 の場合)

式(7)で Y=1 とおけば

$$\int_{-\infty}^{\infty} \frac{\partial f}{\partial t} dv + \int_{-\infty}^{\infty} v \frac{\partial f}{\partial r} dv + \int_{-\infty}^{\infty} \frac{F}{m} \frac{\partial f}{\partial v} dv = \int_{-\infty}^{\infty} \left( \frac{\partial f}{\partial t} \right)_{coll} dv \qquad (9)$$

となる。左辺第1項は、時間偏微分と速度空間積 分を入替えれば

第1項 =

$$\frac{\partial n}{\partial t}$$

(10)

であることが分かる。第2項の速度ベクトルについて、熱平衡ならばその平均値は零である。そこで、熱非平衡における速度ベクトルを非零要素と平均値が零となるような熱バラツキ速度へ分解する。すなわち

$$\mathbf{v} = \mathbf{v}_{d} + \mathbf{u} \tag{11}$$

とする。第2項が平均値を零とするランダム分布 を表わす。式(11)のような分解により式(9)の第 2項は

第 2 項=

$$\nabla(n\mathbf{v}_{d})$$

(12)

となる。第3項は零である。

右辺の緩和項は

$$\int \left(\frac{\partial f}{\partial t}\right)_{coll} d\mathbf{v} = \left(\frac{1}{\partial t} \int f d\mathbf{v}\right)_{coll} = \left(\frac{\partial n}{\partial t}\right)_{coll} \tag{13}$$

であることから、生成再結合項(Generation: G,

Recombination: R, GR 項)であることが分かる。

以上を纏めると式(9)は

$$\frac{\partial n}{\partial t} + \nabla (n \mathbf{v}_d) = G - R \tag{14}$$

となる。良く知られた電流連続式である。

Step 2 運動量保存則 (Y=mv の場合)

式(7)の第2項に速度の自乗項が出現する。統計的平均値が非零となる要素を抽出すれば、第2項は

$$\nabla_r \left( n \overline{m v^2} \right) = \nabla_r \left( n m v_d^2 \right) + \nabla_r \left( n k_B T \right) \tag{15}$$

となる。上式の右辺第2項は熱エネルギーを現している。第1,3項を計算し運動量保存則を導出すると

$$\frac{\partial}{\partial t} (nmv_d) + \nabla (nmv_d^2) + \nabla (nk_B T) - nF$$

$$= \int \left[ mv \left( \frac{\partial f}{\partial t} \right)_{coll} \right] dv$$

(16)

となる。ここでは運動量と密度 n が混在している ので、分離して運動量のみを対象に微分方程式を 記述すると

$$\frac{\partial}{\partial t} (m \mathbf{v}_d) + \mathbf{v}_d \nabla (m \mathbf{v}_d) + \frac{1}{n} \nabla (n \mathbf{k}_B T) - \mathbf{F}$$

$$= -\frac{m \mathbf{v}_d}{\tau_m(w)}$$

(17)

となる。右辺は運動量の緩和時間をライフタイム  $(\tau_m)$ で表現したものである。

Step 3 エネルギー保存則  $(Y = \frac{1}{2}mv^2)$  の場合)

式(7)の第2項が速度の3乗となる。統計的平均値が非零となる要素を抽出すれば第2項は

$$\nabla \left[ n \mathbf{v}_{d} \frac{1}{2} m \left( \mathbf{v}_{d}^{2} + \overline{\mathbf{u}^{2}} \right) + n m \overline{\left( \mathbf{v}_{d} \mathbf{u} \right) \mathbf{u}} \right]$$

$$= \nabla \left( n \mathbf{v}_{d} w + n \mathbf{v}_{d} k_{B} T \right)$$

(18)

となる。一方、ランダムな熱運動を行う粒子のエネルギーは1自由度当 $9 \frac{1}{2} k_B T$ であるので、電子のエネルギー(w)を

$$w = \frac{1}{2} m v_d^2 + \frac{3}{2} k_B T \tag{19}$$

と書くことにすると、エネルギー保存則は

$$\frac{\partial}{\partial t}(nw) + \nabla [nv_d(w + k_B T) - \kappa \nabla T] + qnv_d \mathbf{E}$$

$$= \int_{-\infty}^{\infty} \left[ \frac{1}{2} m v^2 \left( \frac{\partial f}{\partial t} \right)_{coll} \right] d\mathbf{v}$$

(20)

となる。ここでもエネルギーと密度 n が混在しているので、分離してエネルギー成分のみを対象に微分方程式を記述すると

$$\frac{\partial w}{\partial t} + \mathbf{v}_{d} \nabla w + \frac{1}{n} \nabla (n \mathbf{v}_{d} k_{B} T - \kappa \nabla T)

+ q \mathbf{v}_{d} \mathbf{E} = -\frac{w - w_{0}}{\tau_{w}(w)}$$

(21)

となる。右辺はエネルギー緩和の時間 $\tau_w(w)$ で表現してある。なお、本章の詳細は文献[7]を参照して欲しい。

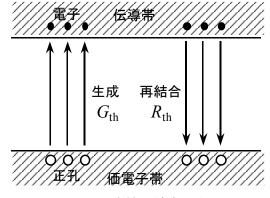

# 1.2. 緩和プロセスとそのモデル化

デバイス動作を記述する基本は電流連続式であり、右辺の GR 項[式(14)]が材料特性を表現する。基本的プロセスは伝導帯と価電子帯の間で発生する『直接遷移型』再結合(図 1 参照)である。熱平衡では生成量と消滅量が釣合い( $G_{th}=R_{th}$ )、GR 項の大きさは零となる。このプロセスが顕著となるのは GaAs のように伝導帯の底が $\Gamma$  谷となる材料である。

図 1 直接再結合過程

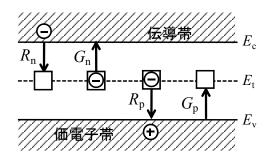

Si のように伝導帯の底が 「谷とならない場合、図 1 に示すようなバンドギャップ中の準位を介した『一準位再結合』プロセスがメインとなる。電子(正孔)の遷移確率は 1) 初期状態でのキャリアの存在確率と遷移先の空席確率との積と、2) 図2に示される4つのプロセスの釣合い条件を現す『レート方程式』により決定される。定常状態であるが、熱非平衡でのキャリア遷移確率を求めたものが、いわゆる SRH [8], [9]モデルと呼ばれるもので、

$$R_{SRH} = \frac{v_{th}\sigma_{n}\sigma_{p}(np - n_{1}p_{1})}{\sigma_{n}(n + n_{1}) + \sigma_{p}(p + p_{1})}N_{T}$$

(22)

と表現される。ただし、熱速度( $\nu_{th}$ )や捕獲断面積 ( $\sigma$ )、準位密度( $N_T$ )を陽に表記せず、ライフタイム ( $\tau$ )で表現した

$$R_{SRH} = \frac{np - n_i^2}{\tau_p(n + n_1) + \tau_n(p + p_1)}$$

(23)

が通常用いられている。

図 2 一準位間接型再結合過程

電子と正孔が再結合するとき、放出エネルギーを他の電子または正孔に与えるようなプロセスを Auger 再結合と言い、以下のようなモデル化がなされている。

$$R_{Aug} = \left(C_n n + C_p p\right) \times \left(np - n_0 p_0\right) \tag{24}$$

デバイス特性へ及ぼす影響として、Si バイポーラトランジスターのエミッター領域で顕著になることが知られている[10]。

再結合の逆となる生成項の内、デバイス特性に大きな影響を及ぼすものとして、雪崩増倍機構がある。高電界中で走行する電子は電界からエネルギーを受け、高エネルギー化する。エネルギーが高くなると価電子帯の電子を伝導帯まで叩き上げ、電子・正孔対を新たに生成するメカニズムである。こうした機構が連続的に起こると電子と正孔が大量に発生し、素子の降伏(Breakdown)が起こる。電子と正孔の動きをみると Auger プロセスと逆の流れになる。電子、正孔を生成する割合(イオン化率: α)は電界強度(E)に強く依存し

$$\alpha = A \exp \left[ -\left(\frac{E_0}{E}\right)^m \right] \tag{25}$$

の形式でモデル化できる。係数  $A, E_0$  は材料固有

のもので、材料ごとにその大きさが知られている。 物性値は文献[7]を参照して欲しい。

# 1.3. キャリア駆動力

半導体内のキャリア駆動である電場(電界)は静電ポテンシャル( $\Psi$ )の勾配(gradient)から決められ、 $\Psi$ はポアソン方程式

$$\nabla(\varepsilon\nabla\Psi) = -\rho \tag{26}$$

より決定される。 $\rho$  は空間電荷密度で、不動電荷 と可動電荷(電子・正孔)より構成される。電子と 正孔の運動方程式とポアソン方程式を連立させ ることでデバイス動作を解析可能とできる。

1.1 節では電子流における保存則を記載した。 正孔流についても同様な結論を得ることができ る。電子と正孔を区別し、改めて電流保存則を記 載すると

$$\frac{\partial n}{\partial t} - \frac{1}{q} \nabla \cdot \boldsymbol{J}_{n} = G - R \tag{27}$$

$$\frac{\partial p}{\partial t} + \frac{1}{q} \nabla \cdot \boldsymbol{J}_{p} = G - R \tag{28}$$

となる。式(26)~(28)のセットが流体モデルによるデバイス解析の基礎式となる。

# 2. 外部因子による生成項

# 2.1. 計算手法

デバイスシミュレータでは、太陽電池やソフトエラーのように、外部からの電磁場や放射線により電子・正孔対が発生する場合の解析が可能である。これら外部因子による定常的な生成量をメッシュファイルに指定しソルバーで読み込む。読み込まれた値は電子と正孔の電流連続方程式(27)、(28)の生成・消滅項(GR項)に反映される。ソフトエラーの過渡解析のように、ある時間だけ電子・生成項が発生するような場合には、その時間だけ生成量を含んだメッシュファイルを使用し、それ以外は生成量を含んでいないメッシュファイルを使用することでシミュレーションが可能となる。

デバイスシミュレータのメッシュファイルに は全格子点での電子正孔対の発生量を $cm^{-3} \cdot s^{-1}$ 単 位で記述する。放射線が入射しない領域には0を 指定する。

# 2.2. 太陽電池デバイスの解析2.2.1. 生成項計算プログラム

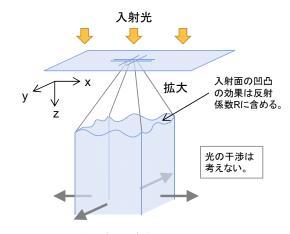

デバイスシミュレータでは、太陽電池の解析用に、太陽光入射による生成項を算出する外部プログラムを備えている。外部プログラムは入射光スペクトル、対象デバイスの屈折率、吸収係数、メッシュファイルを入力として各格子点での電子生成対の生成量を計算しメッシュファイルに追記する。

本プログラムは以下の条件を満たすモデル、も しくは近似的にその条件を満たすモデルを対象 としている。

- XY 方向の境界面の影響は考慮しない。つまり電子正孔対発生量は深さ方向のみに依存することになる。

- 入射面の微小スケールの凹凸の影響は、入射 面の相対屈折率 n に含まれるとする。

- 光の干渉は考えない。

XY方向の境界は考慮しない。

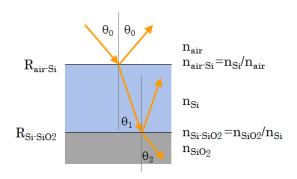

図 3 本プログラムが対象とする太陽電池デバイス模式図

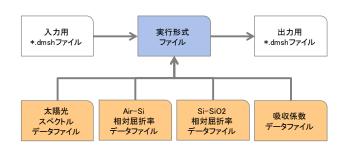

本プログラムのファイル構成を図 4 に示す。本 プログラムは Windows OS 上で動作し、GUI 機能 も含んだ単一の実行形式ファイルである。太陽光 スペクトルデータファイルには波長ごと(単位: nm)の太陽光強度(単位: W/m²/nm)が記述され ている。入射面(Air-Si 界面)相対屈折率データ ファイルには入射面における波長ごとの相対屈 折率 が記述される。反射面 (Si-SiO<sub>2</sub> 界面) 相対 屈折率データファイルには反射面における波長 ごとの相対屈折率 が記述される。吸収係数デー タファイルには波長ごとの Si 基板の吸収係数 (単位:1/cm) が記述される。これらのデータファイルにはデフォルト値がテキスト形式で設定されているが、ユーザーが編集することも可能である。上記4種類のデータファイルは GUI から選択可能である。

図 4 ファイル構成

# 2.2.2. 生成項計算方法

計算は各波長に対して、以下の手順で実行される。光線の角度、反射係数、屈折率の記号の定義は図 5 に示す。

- ① 入射光線の強度 I<sub>0</sub>、入射角 θ<sub>0</sub>、入射面の反射 係数 R<sub>air-Si</sub> から、透過直後の光線の強度 I<sub>1</sub>、 角度 θ<sub>1</sub>を求める。

- ② 吸収係数から光線の軌跡における電子正孔 対発生量を計算する。吸収係数を $\alpha$ とし、光 の進行方向をrとすると、光の強度は  $I_r = I_{r=0} \exp(-\alpha r)$ で表される。ここで光の強 度とは、進行方向に垂直な平面の単位面積に 単位時間あたりに到達する単位波長あたり の光のエネルギーである。これを進行方向の 距離rで微分して符号を入れ替えた

- $-\frac{\partial I}{\partial r} = \alpha I$  が単位体積あたりの吸収エネルギ

ーであり、電子正孔対の発生に使用される。

- ③ 光線がパッシベーション膜( $SiO_2$ )に達した ときには、角度  $\theta_1$ 、Si-  $SiO_2$  界面の反射係数  $R_{Si-SiO_2}$  から、反射される光線の強度  $I_2$  を求める。

- ④ さらに入射面に達したときには、角度 $\theta_1$ 、

R<sub>air-Si</sub>から、反射される光線の強度 I<sub>3</sub>を求める。

- ⑤ 以上のように境界面での反射を繰り返しなが ら計算を続け、光線の強度がある値以下になっ たときに、その波長についての計算を終了する。

- ⑥ 上記の手順を設定した全波長域で計算し、電 子正孔対発生量の合計を計算する。

図 5 光線の角度、反射係数、相対屈折率の定義

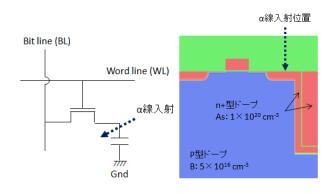

# 2.3. DRAM ソフトエラーの過渡解析2.3.1. 計算モデル

デバイスシミュレータを用いて $\alpha$ 線による DRAM のソフトエラーの発生過程を解析した。 DRAM にビット 1 が書き込まれた状態、つまりキャパシタが正に帯電した状態を初期状態とする。この状態において図 6 左の DRAM 回路図に示す位置に $\alpha$ 線が入射する場合を解析する。図 6 右には計算で使用したモデルと $\alpha$ 線入射位置を示す。 $\alpha$ 線はキャパシタのn+型ドープ領域とSi 基板のp型ドープ領域の間の空乏層にSi 表面に垂直に入射される。

一般的な $\alpha$ 線のエネルギーを  $1\sim10$  MeV 程度とする。保護膜を通過して0.1 MeV までエネルギーが減衰した $\alpha$ 線が Si 表面に到達すると仮定する。この $\alpha$ 線の入射による電子・正孔対発生量、侵入深さ、発生時間などを以下のように概算した。

- Si での電子・正孔対の生成エネルギーを 3.6 eV 程度であるとし、0.1 MeV のエネルギーが 全て生成に使用されたとし、発生量を 28000 個とした。

- 0.1 MeV の α線に対する Si の電子的阻止能を 2.094 × 10<sup>3</sup> MeV/cm とする[11]。侵入深さは入 射エネルギーと電子阻止能による単純な除 算で近似し 0.478 μm とした。

- 0.1 MeV の α線の速度を 2.2×10<sup>6</sup> m/s とし、

0.478 μm の距離を減速せずに進んだと近似し 22 ps の発生時間とした。

- 電子・正孔対は、深さに関係なく、入射方向 に垂直な 10 × 10 nm<sup>2</sup>の断面で発生すると近 似した。

図 6  $\alpha$  線による DRAM のソフトエラー回路図 (左) とモデル (右)

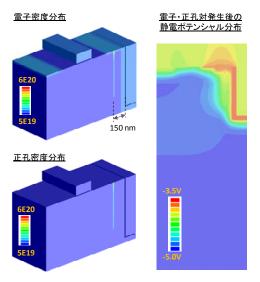

以上のようにした概算した生成量をメッシュファイル内の  $10 \times 10 \times 478 \text{ nm}^3$  の領域に設定し、このメッシュファイルを使用した 22 ps 間の過渡解析を実行し 28000 個の電子・正孔対を発生させた。このときの電子、正孔密度分布と静電ポテンシャル分布を図 7 に示す。

図 7 電子・正孔対発生後の電子、正孔密度と静電ポテンシャル分布

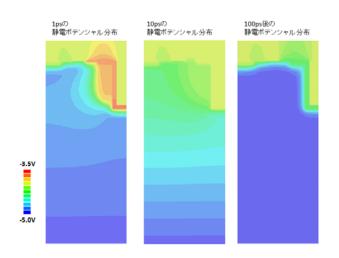

# 2.3.2. 過渡解析計算結果

次に生成項を含んでいないメッシュファイルに戻し、100 ps の時間での過渡解析を実施した。 図 8 c 1、10、100 ps における静電ポテンシャル

分布を示す。空乏層に発生した電子-正孔対のうち、 電子はキャパシタの n+領域に移動し正孔は p 領 域に移動する。1 ps 後では空乏層付近に等電位の 薄オレンジ色の領域が拡がっていることから、生 成時は同じ位置に存在していた電子と正孔が逆 方向に移動していることが分かる。キャパシタの n+領域は、α線入射前の濃いオレンジ色のままで あり、正に帯電した状態が保たれていることを示 す。10 ps 後では、キャパシタの n+領域は薄黄緑 色に変化しており、電子が n+領域に流入している ことを示す。また p 領域では水色の領域が基板電 極の方向に拡大しており、正孔が基板電極に向か って移動していることが分かる。100 ps 後では n+ 領域は濃い黄緑色になっており、発生した電子の 大半が n+領域に移動したことで正の帯電が消滅 し DRAM がビット 0 の状態に変化したことが分 かる。またp領域はα線入射前の電位(青色)に 戻っており、発生した正孔の大半が基板電極へ移 動したことが分かる。

図 8 α線入射後 1 ps (左)、10 ps (中)、100 ps (右) における静電ポテンシャル分布

# 3. バリスティック輸送

#### 3.1. 一般化移動度モデル

デバイス特性を記述する電流保存則を解くには速度  $\nu_d$  を知る必要がある。速度は運動量保存則から式(17)のように決められる。定常状態で且 2次の項を無視すると

$$\mathbf{v}_{d} = -\mu_{n}(w)\mathbf{E} - \frac{D_{n}(w)}{n}\nabla n - \mu_{n}(w)\nabla(\frac{k_{B}T_{e}}{q}) \qquad (29)$$

を得る。ここに $\mu$  とD は

$$\mu_n(w) = \frac{q \, \tau_{me}(w)}{m_e} \tag{30}$$

$$D_n(w) = \frac{k_B T_e}{q} \mu(w) \tag{31}$$

で与えられ、 $\mu$  は移動度と呼ばれる物理量である。 ある程度の長さを走行し、散乱を多数回受け統計 的平均値を持つと、速度は局所的電界強度(E)の値 で決定され

$$v_d(E) = \mu_n E \tag{32}$$

のように表現される。ここではベクトル表現を簡略化してスカラー表現とし、電子の電荷が負であることから、符号を逆転させている。また、不純物をドープすると不純物散乱が移動度を大きく左右するため、不純物濃度を $N_{\rm I}$ と書くことにすると、上式は

$$v_d = v_d(E, N_I) \tag{33}$$

と一般化される。

一方、移動空間が小さく、散乱回数が少ない場合、バリスティック効果が出現する。この効果は局所的電界では一意に決まらず、式(30)に示される如く緩和時間をエネルギーの関数とすることでモデル化できる。ここでエネルギーの関数で表現される非局所的モデルを一般化移動度と呼び、電界の大きさで決めることができる場合を局所モデルと呼ぶことにする。局所モデル、非局所モデルいずれにおいても移動度の大きさを決める因子は運動量緩和時間 $(\tau_m)$ であり、物理的に言えば散乱対象(不純物散乱、フォノン散乱、プラズモン散乱、等)の物性である。また MOSFET の動作では強いゲート電界 $(E_G)$ により電子の存在確率(分布関数)が制御され、散乱事象がバルク中のそれと異なってくるため、MOS 反転層内の移動度は

$$\mu_n = \mu_n (E_D, E_G, N_I) \tag{34}$$

となる。ここに $E_D$ はドレイン方向電界を表わす。 非局所モデルの場合、移動度は

$$\mu_n = \mu_n (w, E_G, N_I) \tag{35}$$

となる。運動量緩和時間に直せば

$$\mu_{n}(w, E_{G}, N_{I}) = \frac{q \tau_{me}(w, E_{G}, N_{I})}{m_{o}}$$

(36)

となる。なお、MOS 反転層内の電流通路はデバイス表面と必ずしも並行ではないので、電界成分の分離は以下のように行う[12]。

$$E_{\mathbf{D}} = (\mathbf{E} \cdot \mathbf{J}) / |\mathbf{J}| \tag{37}$$

$$E_{G} = |\mathbf{E} \times \mathbf{J}| / |\mathbf{J}| \tag{38}$$

上式の物理的意味は、式(20)または(21)に示される如く、ベクトルの内積成分はエネルギー授受を意味し、外積成分はエネルギー授受に関与しないことに相当する。バリスティック輸送のモデル化は式(36)の右辺にある緩和時間を3変数関数として陽に表現することに帰着される。

# 3.2. 緩和係数モデル

シミュレーションを実用的レベルとするには、式(36)あるいは(34)に示されるような3変数関数表を互いの依存性を考慮した上、同時に適性にセットすることが必要となる。しかし、理論的、実験的いずれのアプローチを採用するにせよ、3変数同時アジャストメントは困難である。この課題に対して、Boltzmann 方程式に基礎をおき、変数間の依存性を詳細に調べた Thornber [13] のスケーリング則が助けとなる。スケーリング則に従えば、3変数関数を精度良く1次元変数の集合体に分離可能となる[14]。

スケーリング則の主なる結論は

1) 散乱確率が定数倍(Γ)変化の場合

不純物散乱が支配的要因の場合で、低エネルギー(低電界)状態がこれに相当する。座標と時刻に関する一定比率変換

$$\mathbf{r}_{\Gamma} = \frac{\mathbf{r}}{\Gamma}, t_{\Gamma} = \frac{t}{\Gamma} \tag{39}$$

を考えれば、速度は $\Gamma$ 変換を受けず一定( $\nu_{\Gamma} = \nu$ ) となる。電場はその逆数変換

$$\mathbf{F}_{\Gamma} = \Gamma \mathbf{F} \tag{40}$$

を受け、速度-電界特性に直せば

$$\mathbf{v}_{\Gamma}(\mathbf{E}) = \mathbf{v}(\mathbf{E}/\Gamma) \tag{41}$$

$$\mu_{\Gamma} = \frac{\mu}{\Gamma} \tag{42}$$

となる。移動度が定数倍(Γ)変換される。

2) 運動量スケーリング $(\gamma)$ の場合

運動量はベクトルであるので、スケーリング則 が複雑となる。ここでは結果のみ記すと

$$\mathbf{v}_{A}(\mathbf{E}) = A\mathbf{v}(A^{-1}\mathbf{E}) \tag{43}$$

$$\mu_A = A\mu A^{-1} \tag{44}$$

$$v_{s,t}(\overline{E}) = Av_s(\overline{A^{-1}E}) \tag{45}$$

となる。A の単純ケースとして  $A = \gamma I$  (I: 単位行列)を考えてみると

$$\mathbf{v}_{\gamma} = \gamma \mathbf{v}(\mathbf{E}/\gamma) \tag{46}$$

$$\mu_{v} = \mu \tag{47}$$

となる。移動度に変化がなく、速度は v-E 空間に て同比率変更を受けることになる。

3) 混在スケーリング則

項番 1), 2)を同時に考えるスケーリング則は

$$\mathbf{v}_{\Gamma A}(\mathbf{E}) = A\mathbf{v}(A^{-1}\mathbf{E}/\Gamma) \tag{48}$$

$$\mu_{\Gamma A} = A \mu A^{-1} \tag{49}$$

$$v_{s\Gamma A}(\overline{E}) = Av_s(\overline{A^{-1}E})$$

$$\geq t \gtrsim S_o$$

(50)

緩和時間の逆数を緩和レートまたは緩和係数 と呼ぶ。散乱確率に相当するので、以後の考察で は緩和係数を対象に考えることにする。

MOSFET の動作は反転層内の電子の運動とドレイン近辺でのバルク的運動により構成されている。この2つの運動機構は結果指標であり、シミュレーションを実行するには内部での自動判定を必要とする。前者の緩和係数を $f_{inv}$ 、後者のそれを $f_{bulk}$ と書くことにすると、全緩和係数(r)は $r(w, E_G, N_I) = \max.[f_{inv}(w, E_G, N_I), f_{bulk}(w, N_I)]$

(51)

とモデル化できる。モデル化の主旨は、①電子の 反転層内の運動領域とバルク的運動の領域は異 なるものであるから、独立事象である。②数値計 算モデルとしては値の大きい方で見分けること が可能と言うものである。

ゲート電界( $E_G$ )の存在により電子は反転層内へ閉じ込められ、2次元電子ガス状態(2DEG)を形成する。このため、2次元電子ガスは基板不純物濃度による散乱効果を受けなくなり

$$f_{\text{inv}}(w, E_{\text{G}}, N_{\text{I}}) \approx f_{\text{inv}}(w, E_{\text{G}})$$

(52)

と近似可能となる。式(51)、(52)をみると緩和係数 r は 2 変数関数へ変換できたことが分かる。 さらに、ゲート電界は電子の閉じ込め効果をもたらし、輸送に関与しないことを考えるとスケーリング則から

$$f_{\text{inv}}(w, E_{\text{G}}) \approx \alpha(E_{\text{G}}) \times f_{\text{inv}}(w)$$

(53)

と表現可能なことを理解できる。即ち、1 次元関数の組合せが可能となった。

$f_{\text{bulk}}$  についてもスケーリング則を用いると 2 変数関数の分離が可能となる。低濃度における緩和係数を $\phi(w)$ 、濃度依存を $\gamma(N_1)$ と表現すると

$$f_{\text{bulk}}(w, N_{\text{I}}) = \gamma(N_{\text{I}}) \times \Delta \phi(w) + \phi(w)$$

(54) となる。式(53)、(54)の具体的値を決定するにはモンテカルロシミュレーションを必要とする。ここでは省略する。なお、電子のエネルギー(w)を知る必要があり、これはエネルギー保存則から決める。

# 3.3. 超微細 MOSFET への適用

運動量はベクトルであるため、保存則もベクトルである。このため、電流連続式(スカラー量)を数値解析することに比べ、1 桁以上多くの計算負荷となる。一方、一般化移動度は緩和係数と言うスカラー量でモデル化されると言う利点がある。運動量ベクトルの保存則を数値解析することに比べ圧倒的に少ない計算負荷で済む。

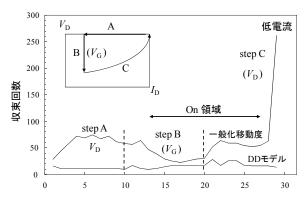

微細 pMOSFET に対し一般化移動度を用いたバリスティック伝導解析と古典的 Drift-Diffusion (DD)モデルを用いた場合の計算時間の比較を図9に示す[15]。バイアススケジュールは次の3ステップ;1) ゲートバイアスは零でドレイン昇圧(step A)、2) ゲート電圧昇圧(step B)、3) ドレイン電圧を零に向かって変化(step C)、からなる一筆書きコースである。

バリスティック効果が顕著になる電流が On となる領域(step B の後半から step C の前半)において一般化移動度モデルでの計算速度が DD モデルのそれと比較し、相対的に高速化することが分かる。逆に、step A や step C のドレイン零バイアス付近(電流 Off 領域)におけるバリスティック

効果が期待できない領域では、一般化移動度モデルの計算速度が低下する。総合すると、バリスティック効果が顕著となる領域で一般化移動度モデルが有効性となり、実用性を理解できる。

図 9 一般化移動度と DD モデルによる計算時間

# 4. 二準位モデル

# 4.1. ダイオード逆方向電流の根源

ダイオードに逆バイアスを印加すれば空乏層 が広がり、空乏層内では

$$np \ll n_i^2 \tag{55}$$

の状態が発生し、式(23)は

$$R_{SRH} \approx -\frac{n_i^2}{\tau_p n_1 + \tau_n p_1} \approx -\frac{n_i}{\tau_g}$$

(56)

となる。再結合率が負(生成項)となり、 $\tau_g$ は生成時におけるライフタイムとなる。上式から分かるように逆方向電流は真性キャリア密度に比例し、ライフタイムに反比例[16]することになる。

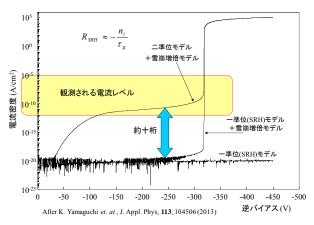

ハイパワー応用に用いられるワイドギャップ 半導体、例えば SiC の場合、真性キャリア密度は 10-9 cm-3 のオーダーとなる。Si のそれが 10<sup>10</sup> cm-3 であることと比べると 20 桁近い差が存在する。 真性キャリア密度の差を考えると、SiC ダイオードの逆方向電流は Si のそれと比較して 10 桁以上小さくなるはずであり、物理的非可測量となる。しかし、現実には Si ダイオードと同程度の逆方向電流が観測されている。この矛盾を克服するべく 2 つの準位を介した生成過程を次の節で述べる。

# 4.2. 二準位間遷移モデル

シリコンでは 1 つの準位が介在する間接型[8], [9]がメインであるため、式(23)のような再結合モ

デルが提案された。しかし、4H-SiC のようにバンドギャップが 3 eV に達すると、準位を 1 つ考えた場合、価電子帯の電子は 1.5 eV ずつの遷移を行い伝導帯へ叩き上げられる必要がある。1.5 eV は Siのバンドギャップよりも大きな値であり、このような遷移は容易には起こらない。一方、ダイオード順方向電流一電圧特性に関する k 値の異常を説明する理論として 2 つの準位を介した間接型モデル[17]の提案がある。しかし、SiC のようなワイドギャップ半導体(~ 3 eV)では 2 つの準位を介しても 1 eV のエネルギー差の遷移を起こす必要があり、単純な二準位モデルでは逆方向電流の見積りは困難である。

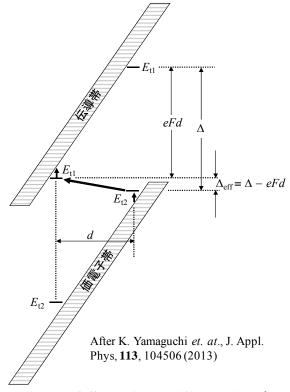

逆バイアスでは空乏層内に強電場が印加される。熱平衡では異なる 2 つの異なる準位( $E_{t1}$ ,  $E_{t2}$ )が強電場中では、図 10 に示すようにほぼ同一レベルになる可能性がある[18]。同一レベルに至った 2 つの準位の空間的距離(d)が小さければホッピング伝導またはトンネル効果による電子遷移が可能となる。

図 10 強逆電場中の二準位間遷移モデル

ホッピング伝導またはトンネル効果による遷移確率を $\omega$ とするとき、2 つの準位を介した生成再結合確率はレート方程式を解くと

$$R_{\omega} = \omega \times f\left(\Delta_{eff}\right) \frac{N_{t1} v_{e} \sigma_{e} N_{t2} v_{p} \sigma_{p}}{X_{1} X_{2} + \eta \omega \times f\left(\Delta_{eff}\right)} \times \left[np - n_{i}^{2} e^{\beta \Delta}\right]$$

(57)

となる[17]。ここに、 $\Delta$ は熱平衡時における 2 つの準位のエネルギー差、 $\Delta$ eff は非平衡時における実効的エネルギー差を表わす(図 10 参照)。また、f は実効的エネルギー差( $\Delta$ eff)が零からズレた場合の遷移確率の変化をガウス関数で近似した

$$f\left(\Delta_{eff}\right) = \exp\left(-\frac{\Delta_{eff}^2}{2\sigma_{ER}^2}\right) \tag{58}$$

で与えられる。なお、 $\beta$ はボルツマン電圧の逆数 である。

# 4.3. 二準位モデルによるダイオード特性解析

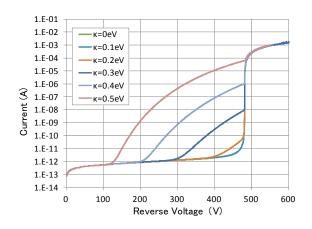

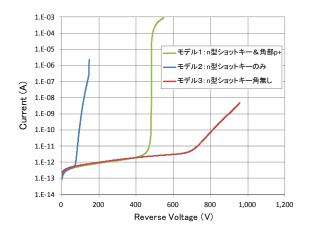

SiC ダイオードにおける逆バイアス特性解析を 行った例を図 11 に示す。一準位モデル、いわゆる SRH モデルから予測される逆方向飽和電流値は  $10^{-20}$  A/cm<sup>2</sup> のレベルとなり、実測される電流値と 10 桁も値が異なるものである。

図 11 図 4.5 SiC ダイオード特性解析

これに対し、二準位モデルに基づく計算値は観測される電流レベルを予測可能としている。二準位モデルの有効性を示すものと考えている。

逆バイアス印加における微弱電流値を精度良く予測可能とすることにより、パワーデバイス特有のガードリング構造、電気的浮遊領域付き構造の解析を可能とすることが期待できる。次節では 浮遊問題について述べる。

# 4.4. フローティング輸送解析

4.3 章で、ワイドギャップ半導体を用いた計算時に発生する逆方向飽和電流が著しく減少する問題を解決する二準位モデルが示された。ここでは、二準位モデルを用いて、電位を固定しない領域を内在させる「ガードリング」と呼ばれる構造を持つものを数値解析した結果を以下に示す。また、二準位モデルを用いても、計算初期において収束性が低いために計算時間がかかってしまうため、それを解決するために仮想ライフタイム法を導入した。

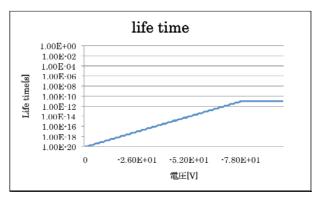

# 4.4.1. 仮想ライフタイム法

ダイオードに逆バイアスを印加した場合、ゼロバイアス近辺の低電圧領域における電流値は極端に低い。このため、電流値が数値計算精度の保証域以下になることがあり、収束性が悪化する。逆耐圧を求める解析を考えた場合、低電圧領域における暗電流計算に計算時間を多用するのは本来の目的から逸脱する。そこで、計算初期において計算の収束性を高めるために、電圧上昇に伴うダンピング領域を設け、電子、正孔のLife-timeに掛ける係数を徐々に変更していく手法を開発した。以下に、仮想ライフタイム法において用いる電子、正孔のライフタイムの式を示す。

$$\tau_{calculation} = \alpha \tau_{true} \tag{59}$$

式の左辺は、計算中に用いる電子、正孔のライフタイムを示し右辺には係数  $\alpha$  と本来用いるべき電子、正孔のライフタイムを示している。計算初期に係数  $\alpha$  を変化させることにより、バイアスステップ初期で電流が殆ど流れない状況において計算の収束性を高め、ある程度バイアスステップが進んだ後に  $\alpha$  を 1 にして計算中に用いる電子、正孔のライフタイムを本来の値に戻す。

次図は、仮想ライフタイム法を用いた場合のバイアスステップ初期におけるライフタイムの変化を示している。バイアスステップが進み電極への印加電圧の変化に伴い、ライフタイムが徐々に変化することにより計算の収束性を高めながら計算を進め、ある程度計算が安定した頃にライフ

タイムを本来の値に戻し、その後は本来の値を用いるためにライフタイムは一定となる。

図 12 仮想ライフタイム法を用いた場合のバイアスステップ初期におけるライフタイムの変化

# 4.4.2. フローティング領域を伴うデバイス解析

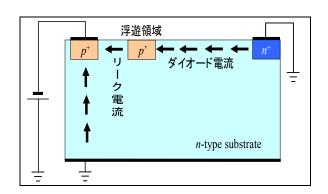

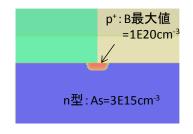

下図に示すような、電位を固定しない領域(浮遊領域)を内在させる「ガードリング」と呼ばれる構造を持つものを数値解析した結果を以下に示す。

図 13 フローティング領域を伴うデバイスの模式図

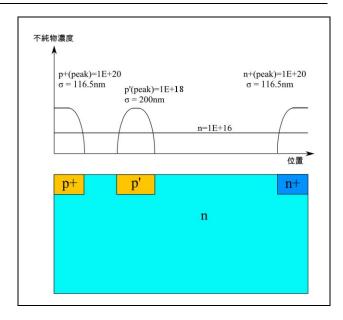

計算に用いた不純物分布は以下に示すようなものを用いた。基盤全体に Sb (アンチモン) を濃度  $10^{16}$  cm<sup>-3</sup> で注入しn 領域を形成、右側の領域に同じく Sb (アンチモン) を濃度  $10^{20}$  cm<sup>-3</sup> で注入しn+領域を形成、そして左側とガードリングに(浮遊領域)に B (ボロン) を濃度  $10^{20}$  cm<sup>-3</sup>,  $10^{18}$  cm<sup>-3</sup> で注入しp+領域とp'領域を形成している。

図 14 不純物分布の模式図

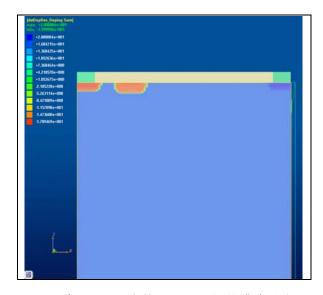

不純物分布作成後に得られる実際の分布を下図に示す。基板材質にはワイドギャップ半導体である SiC を採用し、その上層には SiO2 層を堆積させ、左右に Al 電極を形成しており、SiC 層に n、n+、p+、p'領域が形成されている。

図 15 デバイスの全体図と、不純物濃度分布

次に、作成した計算格子を以下に示す。ここでは、計算精度が必要な「ガードリング」と p+領域周辺では格子密度を高く、それ以外の領域では格子密度を低くして計算全体を効率的に行い、計算時間を短縮させている。計算格子のサイズは、ノード数 16202、要素数 8268 となっている。

図 16 計算格子

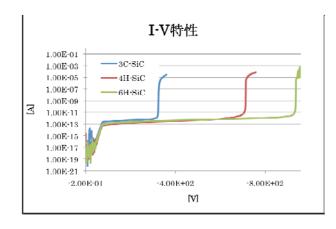

ここまでに作成した、不純物分布と計算格子を用いて逆バイアス計算を行った結果を以下に示す。計算においては、SiC 基板に 3C-SiC、4H-SiC、6H-SiCの3種類の材質を用いて耐圧特性の比較を行った。また、計算技術として、先に述べた仮想ライフタイム法と 4.3 章で述べた二準位モデルを用いている。下図は、計算により得られた I-V 特性を示している。結果は、材質によりブレイクダウン電圧に大きな違いが現れるものとなっており、仮定したイオン化率に即して耐圧に違いが生じていると考えられる。

図 17 フローティング領域を伴うデバイスの模式図

ブレイクダウンの直前と直後でどのようなことが起きているのかを調べるために、4H-SiCを用いた場合の計算におけるブレイクダウン電圧近傍の電子密度分布を以下に示す。

図 18 4H-SiC の計算の印加電圧が-720V (左図) と-722V (右図) の電子密度分布

上図(左)は、ブレイクダウン直前の電子密度分布を示している。p+とp'領域を取り囲むように電子密度の高い領域が分布しており、そこから p+領域へと若干密度の高い領域が接続している。一方、上図(右)は、ブレイクダウン直後の電子密度分布を示している。ブレイクダウン直前よりも、p+とp'領域を取り囲む高密度領域と p+領域との間を接続している領域の密度が上がり、電流が流れて始めブレイクダウンが発生したことが確認できる。ここで行った逆バイアス計算に要した計算時間を以下に示す。用いた材質より計算時間が異なるのは、ブレイクダウン電圧が異なるためである。

表 1 材質ごとの計算時間(使用 CPU:Intel Xeon E31225@3.1Ghz)

| 材質     | 計算時間[sec] |

|--------|-----------|

| 3C-SiC | 25445.06  |

| 4H-SiC | 29364.83  |

| 6H-SiC | 30486.37  |

#### 4.4.3. まとめ

ワイドギャップ半導体(SiC)における浮遊電 位解析を安定的に実施可能な手法の開発を行い、その計算結果を示した。3 種類のワイドギャップ 半導体、3C-SiC、4H-SiC、6H-SiC を用いた逆バイアス計算により、仮定したイオン化率に即して耐圧に違いが生じる結果を得た。また、ブレイクダウンの発生近傍では、印加電圧のわずかな違いで、電子の密度分布が大きく変化する結果を計算結果の描画によりそれを確認することができた。計

算時間については、4.7 章で示すバイアスの粗密 調整機能を利用することにより、表 1 で示した時 間よりさらに 1/2 程度の短縮が可能となっている。

# 5. パワーデバイス用の解析機能

# 5.1. はじめに

デバイスシミュレータでは、パワーデバイスの解析に必要な機能を開発してきた。本稿では、そのうち、ショットキー電極モデル、バイアスの粗密調整機能、高耐圧計算用の機能について説明する。

# 5.2. ショットキー電極モデル

# 5.2.1. 電極モデル

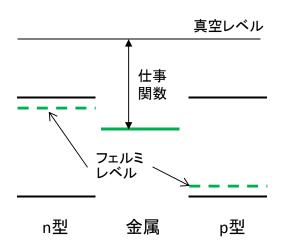

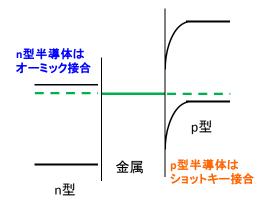

デバイスシミュレータでは、電極金属と半導体の接合のモデルとして、オーミック接合、n型ショットキー接合、p型ショットキー接合の3種類のモデルが選択可能である。この3種類の接合を説明するため、電極金属にn型とp型の半導体が接合する場合を考える。接合前の金属の仕事関数と半導体のフェルミレベルは図19に示す高低関係にあるとする。

図 19 接触前の電極金属仕事関数と n、p型 半導体のフェルミレベルの高低関係

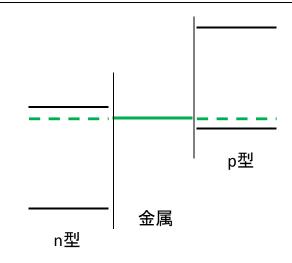

オーミック接合モデルを選択した場合には、図 20 に示すように n、p 型の両半導体のバンドは曲 がることなく金属に接合する。またフェルミレベルのバンドに対する相対高さは接合前と変化しない。

図 20 オーミック接合モデルにおけるバンド図

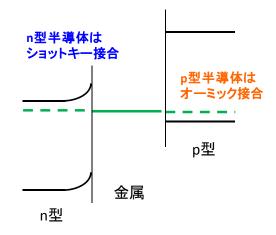

n 型ショットキー接合モデルを選択した場合には、図 21 に示すように、n 型半導体はショットキー接合となり、p 型半導体はオーミック接合となる。

図 21 n型ショットキー接合モデルにおける バンド図

図 22 p型ショットキー接合モデルにおける バンド図

p型ショットキー接合モデルを選択した場合に

は、図 22 に示すように、p 型半導体はショット キー接合となり、n 型半導体はオーミック接合と なる。

# 5.2.2. ショットキー電極モデル

デバイスシミュレータでは、ショットキー接合 電極におけるトンネル電流と熱電子放出のモデ ルが使用可能である。

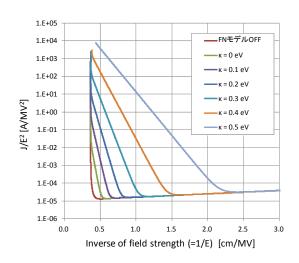

トンネル電流モデルには式(60)に示す Fowler-Nordheim (F-N) モデルを採用した。

$$J_{FN} = AE^{n} \exp\left(-\frac{B}{E}\right)$$

$$B = \frac{4\sqrt{2m}}{3q\hbar} (q\phi_{B} - q\kappa)^{3/2}$$

(60)

ここで A、n、m、 $\kappa$  はユーザーによる入力パラメータとしている。 $\phi_B$  はバンド障壁の高さであり、電極金属の仕事関数と半導体の電子親和力から計算される。また  $\kappa$  はバンドの障壁低下量を表す。

熱電子放出モデルには式(61)のモデルを採用した。 $A_R$ はリチャードソン定数 (=  $120 \text{ A/cm}^2/\text{K}^2$ )である。

$$J_{TE} = J_{ST} \left[ \exp\left(\frac{qV}{k_B T}\right) - 1 \right]$$

$$J_{ST} = A_R T^2 \exp\left(-\frac{q\phi_B}{k_B T}\right)$$

(61)

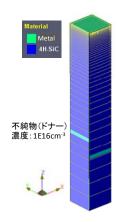

ショットキー電極モデルの検証計算として、図 23 に示す簡易モデルで逆バイアスでの電流特性 を取得した。

図 23 ショットキーモデル検証用計算

モデルは 4H-SiC の上部に金属電極がショットキ

一接続しており、サイズは  $1 \mu m \times 1 \mu m \times 7 \mu m$  である。 $1 \times 10^{16} \text{ cm}^{-3}$  のドナーがドーピングされている。障壁高さが 0.8 eV となるように、電極の仕事関数を 4.92 eV、4H-SiC の電子親和力を 4.12 eV とした。また F-N モデルパラメータとして以下の値を使用した。

- $A = 2 \times 10^{-6} \text{ A/V}^2$

- n = 2

- m = m<sub>0</sub> (電子の静止質量)

- $\kappa = 0.2 \text{ eV}$

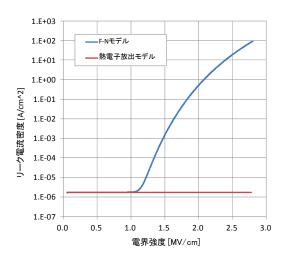

0~1500 Vまでの逆バイアスを印加したときの電界強度とリーク電流密度の計算結果を図 24 に示す。

図 24 ショットキー電極リーク電流モデルの電界強度依存性

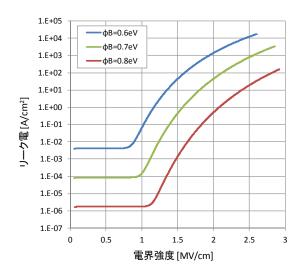

図 25 F-N モデルの障壁高さ依存性 次にF-Nモデルのショットキー障壁高さへの依

存性を確認するため、障壁高さ $\phi_B$ が 0.6、0.7 eV となるように金属の仕事関数を変化させた。計算 結果を図 25 に示す。

次に障壁高さ $\phi_B = 0.8 \text{ eV}$  で、障壁低下 $\kappa$  を変化させたときの結果を図 26 に示す。

図 26 F-N モデルの障壁低下量依存性

# 5.2.3. 角のある電極の解析事例

# (1) 計算モデル

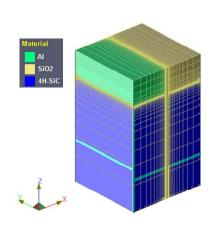

ショットキー電極モデルの解析事例として、図 27 に示すような 4H-SiC に角のある電極が接続している場合の解析結果を示す。

図 27 角のある電極のモデル

モデルは 4H-SiC の上部に  $1.5~\mu m \times 3~\mu m \times 1~\mu m$  の金属電極が接続している。4H-SiC のサイズは  $3~\mu m \times 3~\mu m \times 4~\mu m$  である。4H-SiC のドーピングプロファイルを図  $28~\epsilon r$ 。 $3\times 10^{15}~\epsilon r$ 。 $0~\epsilon r$  のドナーをドーピングし、電極角部には電界緩和用に  $1\times r$

$10^{15} \,\mathrm{cm}^{-3}$  のアクセプターをドープした。

図 28 ドーピングプロファイル

電極モデルはn型ショットキー接合モデルを選択した。これによりn型領域とはショットキー接合、電極角部のp+領域とはオーミック接合することになる。ショットキー接合の障壁高が0.8 eVとなるように、電極の仕事関数と4H-SiCの電子親和力を設定した。またF-Nモデルパラメータとして以下の値を使用した。

- $A = 2 \times 10^{-6} \text{ A/V}^2$

- n = 2

- m = m<sub>0</sub> (電子の静止質量)

- $\kappa = 0 \sim 0.5 \text{ eV}$

# (2) 計算結果

$0\sim600~V$  までの逆バイアスを印加したときの障壁低下量 $\kappa$ のリーク電流値への依存性を図 29に示す。障壁低下 $\kappa$ が大きいほどリーク電流の耐圧が小さくなる。 $\kappa=0.5~eV$ では 130 Vの逆バイアスでリーク電流が増大し始める。なお、 $\kappa=0.1~eV$  以下では電流プロファイルは一致し、逆バイアスが 480 V で電流が増大している。この 480 V のリーク電流は F-N 電流によるものではなく、アバランシェ降伏による電流である。

次に電極角部の p+ドーピングによる電界緩和の影響を確認するため、これまでのモデルをモデル1とし、p+をドーピングしない場合と電極が全面を覆っていて角がないモデルをそれぞれモデル2、3として、 $\kappa=0$  V での耐圧を比較した。0 ~1000 V までの逆バイアスを印加したときの印加バイアスとリーク電流の計算結果を図 30 に示す。

図 29 障壁低下量κのリーク電流依存性

図 30 逆バイアス電流特性

リーク電流に対する耐圧は、モデル 2、モデル 1、モデル 3 の順となった。電極角部に p+領域のないモデル 2 では  $80\ V$  を超えたあたりから電流が増加するのに対し、モデル 2 は  $400\ V$  までは角のないモデル 3 と同じ量のリーク電流しか流れない。これはモデル 2 の電極角部の p+領域が電界を緩和したためである。

#### 5.2.4. まとめ

本稿では、デバイスシミュレータが有するパワーデバイスの解析に必要な機能のうち、ショットキー電極モデル、バイアスの粗密調整機能、高耐圧計算用の機能について説明した。

#### 5.3. バイアスの粗密調整

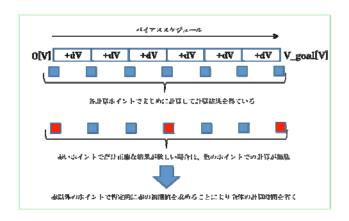

バイアス粗密調整とは、デバイスシミュレーション実行における高速化手法の1つである。下図

に示すように、通常は電極電圧の昇圧を複数のス テップに分けて徐々に行う。その際、各ステップ の計算時に、方程式を行列の緩和法を用いて解く ことによりポテンシャル分布と、電子、正孔の密 度を求めている。一方で、ユーザーが各ステップ ごとに計算結果を必要とする場面はそれ程多く なく、結果が必要なステップにおいて正確な値が 得られれば十分な場合が多く存在する。そこで、 全てのバイアスステップにおいて指定の残差に なるまで解を求めるのは止めて、結果が必要なバ イアスステップにおいてのみ指定の残差になる まで解を求めれば、計算速度の向上に繋がる。言 いかえれば、正確な結果が必要なバイアスステッ プ以外の計算で、暫定的に、正確な結果が必要な バイアスステップにおける初期値を求めること により全体の計算時間を省くことになる。ここで 必要となるのは、正確な結果を必要とするバイア スステップの間隔と、それ以外のステップにおけ る収束判定残差をどの程度に設定すれば最も高 速化の効率が良いかを調査することである。ここ では、バイアスステップの間隔は数10倍 程度に 設定しておき、基本的なダイオードの耐圧計算に おいて、正確な結果を必要とするステップ以外に おける収束判定残差の値による計算速度の違い を測定する。また、そこで得られた結果を参考に、 4.4.2 節で示したフローティング領域を伴うデバ イス解析で行った計算におけるバイアス粗密調 整の効果を示す。

図 31 バイアス粗密調整の説明図

# 5.3.1. ダイオード計算におけるバイアス粗密調整 の効果

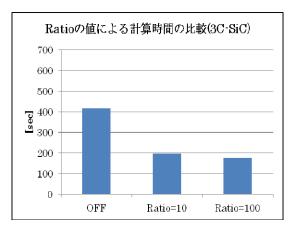

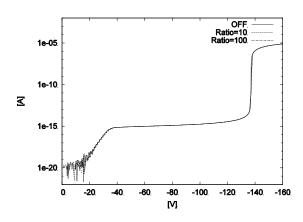

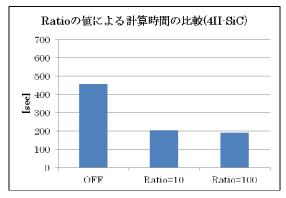

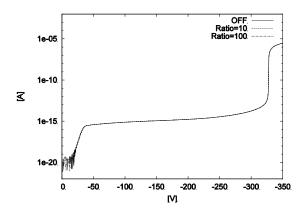

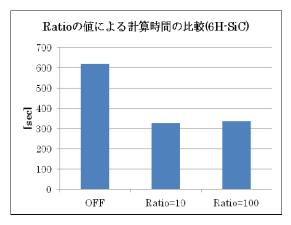

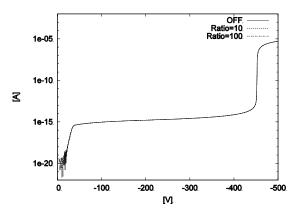

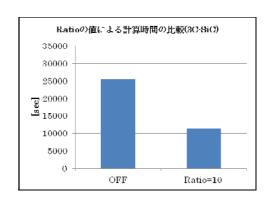

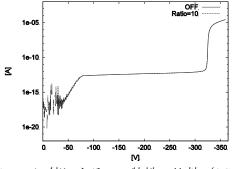

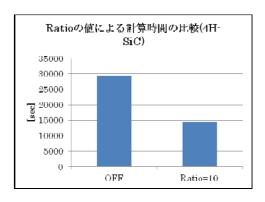

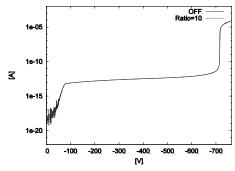

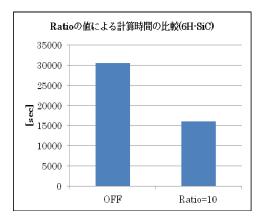

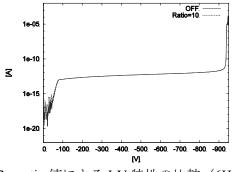

ここでは、簡単な例として、pn 接合ダイオードの耐圧計算を行った場合の計算時間について、バイアス粗密調整の機能を off にした場合、正確な値を必要とするバイアスステップとそれ以外のステップににおける収束判定値に対する割合 ratio が 10 の場合と 100 の場合の比較を行った結果を示す。また、半導体材料については、3C-SiC、4H-SiC、6H-SiC を用いた結果をそれぞれ示す。

図 32 ratio 値による計算時間の比較(3C-SiC)

図 33 ratio 値による I-V 特性の比較(3C-SiC)

図 34 ratio 値による計算時間の比較 (4H-SiC)

図 35 ratio 値による I-V 特性の比較 (4H-SiC)

図 36 ratio 値による計算時間の比較 (6H-SiC)

図 37 ratio 値による I-V 特性の比較 (6H-SiC)

各半導体材料における ratio 値による計算時間の比較を示した図 32、図 34、図 36より、半導体材料に関わらず、ratio=10 の場合にはバイアス粗密調整を off にした場合の約半分程度の計算時間で結果が得られていることが分かる。ratio=10の場合については、どの材料においても ratio=10の場合とほぼ同じ計算時間となっており、ratio=10の場合と同等の効率アップとなっている。バイアス粗密調整を行った場合の計算結果については、

図 33、図 35、図 37 に示した I-V 特性において、 半導体材料に関わらずバイアス粗密調整を off に した場合の結果と ratio=10,、ratio=100 の両結果共 に遜色ない結果が得られている。ここまでの結果 から、計算対象にもよるが、ratio の値は 10 以下 に抑えておくと、高い高速化効率が得られると考 えられる。ここで用いたバイアス粗密調整のステ ップ間隔は 20 となっている。

# 5.3.2. Floating 領域を含む計算におけるバイアス 粗密調整の効果

簡単な pn 接合ダイオードを用いた耐圧計算で行ったバイアス粗密調整の計算結果から、正確な値を必要とするバイアスステップとそれ以外のステップにおける収東判定値に対する割合 ratioが 10 近辺で高い高速化効率が得られることが分かった。その結果を踏まえ、4.4.2 節で行ったフローティング領域を伴うデバイス解析について、バイアス粗密調整を off にした場合と ratio=10 にして計算した場合の計算時間の比較を行った結果を示す。基板材質についての違いもダイオード計算時と同様に比較するため、3C-SiC、4H-SiC、6H-SiC について計算を行った。

図 38 ratio 値による計算時間の比較 (3C-SiC)

図 39 ratio 値による I-V 特性の比較(3C-SiC)

図 40 ratio 値による計算時間の比較 (4H-SiC)

図 41 ratio 値による I-V 特性の比較(4H-SiC)

図 42 ratio 値による計算時間の比較 (6H-SiC)

図 43 ratio 値による I-V 特性の比較 (6H-SiC)

図 38、図 40、図 42 より、簡単な pn 接合ダイオードの耐圧計算で得られた結果と同様に、基板材料が 3C-SiC、4H-SiC、6H-SiC について、バイアス粗密調整が off の場合に対して、ratio=10 でバ

イアス粗密調整を行った場合で約2倍の計算時間の高速化を達成しており、どの材料においてもバイアス粗密調整機能により計算速度が上がる結果を得た。計算結果については、図39、図41、図43において、3つの基板材料について、バイアス粗密調整をoffの場合と、ratio=10でonにして計算した場合に得られたI-V特性を比較している。基板材料が3C-SiC、4H-SiC、6H-SiC それぞれにおいて、グラフは殆ど重なっており、バイアス粗密調整をoffにした場合とonにした場合とで、殆ど違いがないことが確認できる。以上のことから、バイアス粗密調整機能により結果は変わらずに約2倍早く計算結果を得られるという結果が得られた。ここで用いたバイアス粗密調整のステップ間隔は20となっている。

#### 5.3.3. まとめ

ここで示したバイアス粗密調整機能を用いることにより、機能を off にした場合に比べて約 2 倍の計算時間の高速化が可能となることを示した。また、機能を on にした場合でも、得られる計算結果に違いはないことも確認を行った。ここでは、計算例として、簡単な pn 接合ダイオードと Floating 領域を含む計算について得られた効果について示したが、これ以外の計算対象においても、同様に高速化の効果が期待できると考えている。

#### 5.4. 高耐圧計算

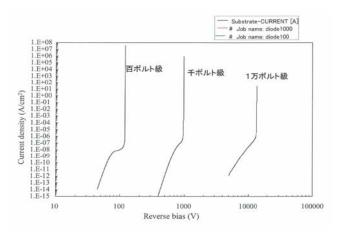

# 5.4.1. 4H-SiC を用いたダイオードの耐圧計算

パワー半導体のデバイス解析においては、高耐圧計算が必要となる場面が、微細デバイスの解析時よりも多くなると予想される。そこで、今回開発したデバイスシミュレータの高耐圧計算性能の調査を兼ねて、耐圧が 100[V]級、1000[V]級、1000[V]級のものと、3 つのダイオードの計算を行い、得られた I-V 特性を以下に示す。計算には、半導体材料として 4H-SiC を用い、ダイオードの長さは 100[V]級が  $0.4[\mu\,m]$ 、1000[V]級が  $4[\mu\,m]$ 、10000[V]級が  $80[\mu\,m]$ と、耐圧を上げるために役 10 倍程度ずつ長くしている。結果は、どの計算に

おいてもブレイクダウンまで計算が可能であり、 開発したデバイスシミュレータが、広バイアスレ ンジに対応していることを同時に示している。

図 44 4H-SiC を用いたダイオードの耐圧計算

#### 5.4.2. まとめ

ここで得られた結果は、我々が開発したデバイスシミュレータが、高耐圧であるとして期待されている SiC 系の半導体材料を用いた、広バイアスレンジの耐圧シミュレーションが可能であることを示している。これにより、今回開発したシミュレータが、パワー半導体を用いた計算により多く利用されるように活動を行っていく。

#### 6. 複数トランジスタの一括解析

# 6.1. はじめに

複数のトランジスタとその間の配線を一括してデバイスシミュレーションすることにより、従来の手法であるミックスモードシミュレーションでは容易に解析できなかった、寄生抵抗や寄生容量の影響を簡単に解析することが可能となった。ここでは、一括解析に必要な計算手法を紹介すると共に寄生容量の影響が顕著に現れるインバータチェーンの遅延動作の解析事例を紹介する。

大規模集積回路 (LSI) は 1965 年にゴードン・ムーアが提唱した予測[19]に従いながら、今日まで高集積化と高密度化を続けてきた。2014 年にはインテルが 14nm のデザインルールのプロセスを発表するまでに微細化が進んでいる。

微細化が進むにつれ、MOS トランジスタ間の電 気的な相互作用を無視することはできない。シミ ュレーションにおいても同様であり、複数のデバイス部品(トランジスタやダイオードなど)からなる系については、部品単体の特性だけでなく、それらを接続する配線は接続部の寄生抵抗や、配線やデバイス間の寄生容量の影響も考慮する必要がある。

通常の複数デバイスの解析では、個々のデバイス部品を回路接続するミックスモードシミュレーション[20]が用いられている。相互作用の解析精度はユーザーがあらかじめ設定する寄生抵抗や寄生容量に依存し、寄生容量を高精度に求めるには構造3次元の容量解析を事前実行する負担がユーザーに課せられていた[21][22]。

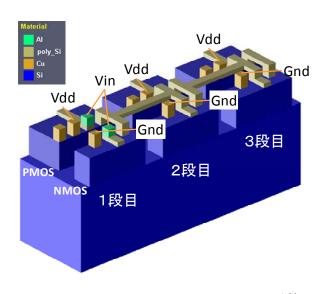

今回、複数のトランジスタとそれらを接続する配線からなる系を一括してデバイスシミュレーションできる手法を開発した。寄生抵抗や寄生容量はデバイスシミュレーションで計算されるため、ユーザーが事前に値を準備しておく必要はない。本手法をデバイスシミュレータに取り込みインバータチェーンの過渡解析を実施した。

# 6.2. 計算手法

# 6.2.1. 内部配線モデル

デバイス間の配線をデバイスシミュレーションの方程式の枠組みの中で扱う手法を新たに開発し取り込んだ。

デバイスシミュレーションはポアソン方程式 (過渡解析の場合にはその時間微分式)、電子と 正孔の 2 つの電流連続方程式を解き、静電ポテンシャル $\phi$ 、電子密度 n と正孔密度 p を解として得る。金属は電極として $\phi$ 、n、p のディリクレ境界条件として現れるのみである。金属の電気伝導を表すオームの法則  $J=\sigma$  E をこの解法の枠組みの中に取り込むことは容易ではない。

そこで、金属を狭いバンドギャップの半導体と みなすことでモデル化した。

# 6.2.2. 過渡解析

遅延特性を解析するために過渡解析を実施した。デバイスシミュレータの過渡解析は、ポアソン方程式の時間微分式と電子および正孔それぞ

れの電流連続方程式からなる三式の連立方程式 を構成式とする。これら三式を完全陰解法により 反復計算することにより静電ポテンシャル、電子 および正孔密度を得る。過渡解析の詳細について は別稿にて説明する。

$$\frac{\partial}{\partial t} \left[ -\nabla \cdot \left( \varepsilon_s \nabla \psi \right) \right] + \frac{q}{\varepsilon_0} \left( \nabla \cdot J_n + \nabla \cdot J_p \right) = 0 \tag{62}$$

$$\frac{\partial n}{\partial t} = \frac{1}{q} \nabla \cdot J_n - R \tag{63}$$

$$\frac{\partial p}{\partial t} = -\frac{1}{q} \nabla \cdot J_p - R \tag{64}$$

# 6.3. 計算事例

# 6.3.1. E/D NMOS インバータチェーンの解析

これまでに実施した複数トランジスター括解析の適用例の1つ目として、enhancement/depletion (E/D) NMOS インバータチェーンの一括過渡解析について紹介する。

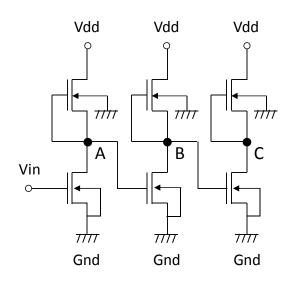

# (1) E/D NMOS インバータチェーン

解析対象となる 3 段の E/D NMOS インバータチェーンの回路図を図 45 に示す。以降の説明の便宜上、各段の上下の NMOS 間の配線上の点を A、B、C とする。上段の 3 つのトランジスタはデプレッション型 NMOS であり、ゲートーソース間の電位差 Vgs が 0 V であってもトランジスタがオンの状態となる (ノーマリーオン)。図 45 に示すように E/D インバータのデプレッション型 NMOSのゲートはソースと結線されており、常にオン状態となる。下段の 3 つのトランジスタはエンハンスメント型 NMOS であり、Vgs が 0 V ではオフ状態 (ノーマリーオフ)となっているが、Vgs > 0 Vでトランジスタがオンする。Vgs の大小でオン抵抗が変化する。

Vin が 0 V (= Vgnd) の時には、1 段目のエンハンスメント型 NMOS はオフ状態となる。デプレッション型 NMOS はノーマリーオン状態であるため点 A の電位は Vdd となる。点 A を含む配線は 2 段目のエンハンスメント型 NMOS のゲートに結線されており、この NMOS がオン状態となる。ドーピングを調整することで、エンハンスメント型

NMOS のオン抵抗がデプレッション型 NMOS のオン抵抗よりも大きくすることで点 B の電位は Vgnd となる。点 B を含む配線は 3 段目のエンハンスメント型 NMOS のゲートに結線されている。 3 段目の動作は 1 段目と同様である。

図 45 3段 E/D NMOS インバータチェーン回路図

# (2) 計算モデルと解析条件

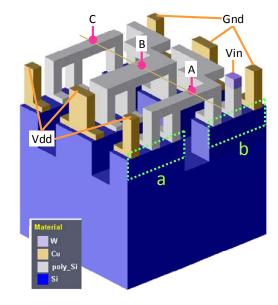

デバイスシミュレータ用の計算モデルを図 46 に示す。便宜上、ゲート酸化膜と配線間酸化膜は 非表示とした。点線で囲まれた領域 a と b は、それぞれ 1 段目のデプレッション型 NMOS(図 45 の左上の NMOS)とエンハンスメント型 NMOS(図 45 の左下の NMOS)の断面を示している。 ゲート長は 200 nm、ゲート酸化膜厚は 10 nm とした。ゲート幅は 1 段目と 3 段目が 250 nm、2 段目は 500 nm とした。図 45 の A、B、C に対応する点を図 46 にも示したが、以降の計算結果における計算値はこの点において取得した。

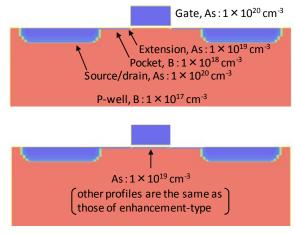

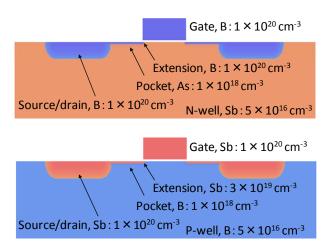

エンハンスメント型 NMOS(図 46 の断面 b)とデプレッション型 NMOS(図 46 の断面 a)のドーピングプロファイルを図 47 の上と下に示す。デプレッション型 NMOS はエンハンスメント型 NMOS のドーピングに加えて、ゲート直下にヒ素を  $1 \times 10^{19}$  cm<sup>-3</sup> の濃度で注入することによりノーマリーオン状態となる。この濃度ではオン抵抗がエンハンスメント型 NMOS のオン抵抗より小さくなる。

図 46 3 段 E/D NMOS インバータチェーンの 計算モデル (※酸化膜は非表示)

図 47 エンハンスメント型 NMOS (上) と下デプレッション型 NMOS (下) のドーピングプロファイル

解析はまず Vin=0 V、Vdd=2 V、Gnd=0 V の 状態を定常状態計算で求める。次に、時刻 t=0 秒において Vin に 2 V をステップ状に印加し、それ以降の時刻における過渡解析を実施した。

# (3) 計算結果

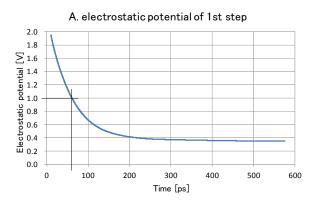

図 48 にインバータの出力である A、B、C 点における静電ポテンシャルの時間変化を示す。なお各データについて  $0\sim10$  ps ではパルス上のピークが見られたため非表示とした。このピークは Vin  $\sim$  のステップ状のバイアス印加、つまり t=0 秒で瞬間的に  $V\to 2$  V に昇圧したことによる。現実的には瞬間的に昇圧することは不可能であり、以

降の議論において関係ないため非表示とした。

A、B、Cの順で静電ポテンシャルが反転している。点 A では Vin へのバイアス印加後 10 ps の時点で静電ポテンシャルが 2 V から下がり始めている (反転し始めている)。80 ps では点 B が、120 ps では点 C が反転を開始する。点 A と点 C では反転開始後およそ 200 ps の時間で変化しているのに対し、点 B では 400 ps 以上の時間を要している。 2 段目の NMOS のゲート幅が 1、3 段目よりも 2 倍の大きさであることから寄生容量も同様に大きくなることで時定数が大きくなったためである。

図 48 A、B、C 点における静電ポテンシャルの 時間変化

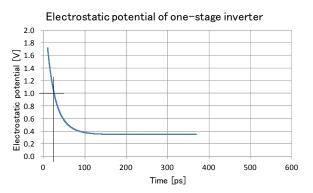

参考データとして、1段目のインバータのみを 取り出したモデルでの静電ポテンシャルの時間 変化を図 49 に示す。静電ポテンシャルが 1 V に達するまでの時間を比較すると、図 48 の A では60 ps であるのに対し、図 49 では25 ps である。これは2 段目、3 段目のインバータによる寄生抵抗や寄生容量の影響の有無の差である。このように一括解析では寄生抵抗や寄生容量の影響を簡単に再現することが可能となる。

図 49 A、B、C 点における静電ポテンシャルの時間変化

# 6.3.2. CMOS インバータチェーンの解析

複数トランジスター括解析の適用例の2つ目として、CMOSインバータの一括過渡解析について紹介する。

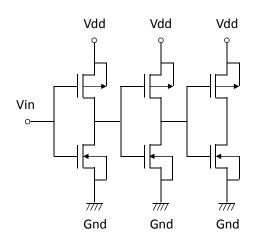

#### (1) CMOS インバータチェーン

解析対象となる 3 段の CMOS インバータチェーンの回路図を図 50 に示す。上段の 3 つのトランジスタはエンハンスメント型で PMOS であり、下段の 3 つのトランジスタはエンハンスメント型で NMOS である。PMOS は Vin = Vdd のときにオフ状態であり Vin < Vdd でオン状態に移行し、NMOS は Vin が Vin のときにはオフ状態であり Vin でオン状態に移行する。

Vin が 0 V (= Vgnd) の時には、1 段目の PMOS はオン状態、NMOS はオフ状態であるためインバータの出力となる NMOS-PMOS 配線の電位はおよそ Vdd となる。これが 2 段目のインバータの入力となり、2 段目の PMOS がオフ状態、NMOS はオン状態となり出力はおよそ Vgnd となる。これを入力とする 3 段目の動作は 1 段目と同様である。

図 50 3段 CMOS インバータチェーン回路図

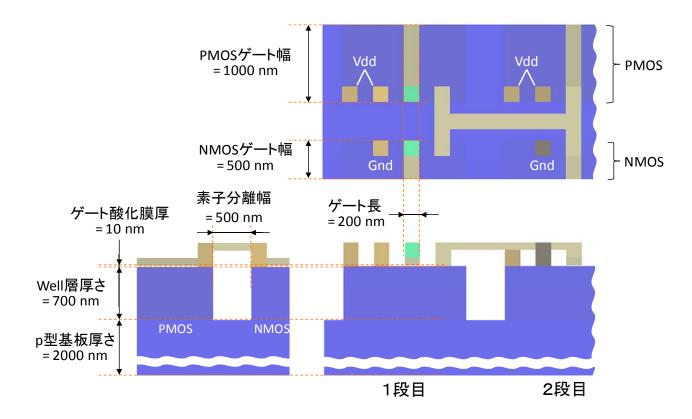

# (2) 計算モデルと解析条件

デバイスシミュレータ用の計算モデルの俯瞰 図を図 51 に示す。便宜上、ゲート酸化膜と配線 間酸化膜は非表示とした。左から1、2、3 段の順で CMOS インバータが配置されている。手前の3つのトランジスタが NMOS であり 奥側の3つのトランジスタが PMOS である。図 54 には代表的な 寸法を示す。PMOS のゲート幅を NMOS のゲート幅の2倍とした。

図 51 3段 CMOS インバータチェーンの計算 モデル俯瞰図 (※酸化膜は非表示)

$1 \times 10^{16}~{\rm cm}^{-3}$  のボロンで一様にドーピングした P 型基板上に N-well、P-well 層を設け PMOS と NMOS を形成した。ドーピングプロファイルを図 52 に示す。PMOS と NMOS のデバイス特性を反

対称に近づけるため、Extension の濃度を調整した。PMOS の Extension にはボロンを  $1\times10^{20}$  cm<sup>-3</sup> でドーピングし、NMOS の Extension にはアンチモンを  $3\times10^{19}$  cm<sup>-3</sup> でドーピングした。

図 52 PMOS (上) と NMOS (下) のドーピング プロファイル

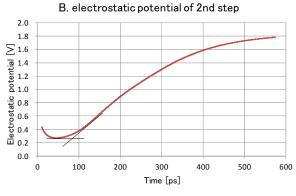

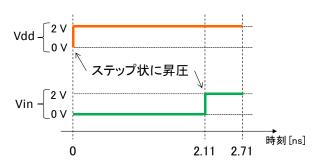

解析はまず時刻 t=0 秒において Vdd に 2 V を ステップ状に印加し、2.1 ns 間の過渡解析を実施し定常状態を得る。次に 2.1ns において Vin に 2 V をステップ状に印加する。これ以降 0.6ns 間の過渡解析を実施した。

図 53 過渡解析バイアス印加方法

図 54 3 段 CMOS インバータチェーンの計算モデル平面図 (※酸化膜は非表示)

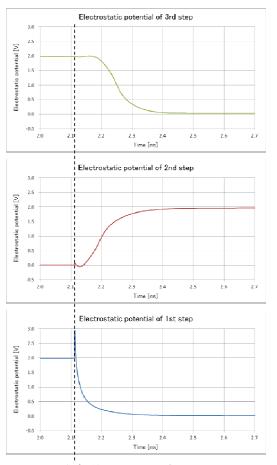

# (3) 計算結果

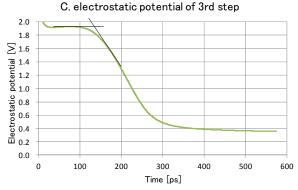

図 55 に Vin 印加後の静電ポテンシャルの時間変化を示す。Vin 印加直後にパルス状の変化が 1段目に顕著にみられるが、これは t=2.11 ns で瞬間的に 0 V  $\rightarrow$  2 V に昇圧したことによる。

1、2、3 段目の順で静電ポテンシャルが反転している。1 段目は Vin へのバイアス印加後すぐに (0.01 ns のオーダーで) 静電ポテンシャルが 2V から下がり始めているのに対し、2 段目は 0.3 ns 後から、3 段目は 0.6 ns 後から下がり始める。

なお、E/D NMOS インバータのモデルと異なり、 各段の NMOS のサイズを同一にしているため、反 転終了までの時間が段ごとに大きく異なること はなかった。

図 55 Vin 印加後 0.6 ns 間  $(t = 2.11 \sim 2.71$  ns) の各段の静電ポテンシャルの時間変化

# 6.4. 今後の課題

今回開発した内部配線モデルは、半導体の物性値を変えることで金属としてみなしたモデルである。実際の金属の抵抗値や金属と半導体の接触抵抗などの値と定量的に一致させるためには、金属ごとにパラメータの合わせ込みが必要である。合わせ込むべきパラメータの選択やその方法については今後の課題である。

またデバイスシミュレータでは大規模で高速な計算を目的とした開発も進めており、これらを使用してさらに大規模で長いタイムスケールでの計算も行う予定である。

# 6.5. まとめ

本稿では、デバイスシミュレーションによる複数トランジスター括解析について、その手法と解析事例について示した。本手法はデバイス間の寄生抵抗や寄生容量による影響を簡単にかつ高精度で取り込み、高集積化、高密度化を続ける LSI のデバイス特性に有効な手法である。

# 7. 並列計算

# 7.1. 並列計算手法

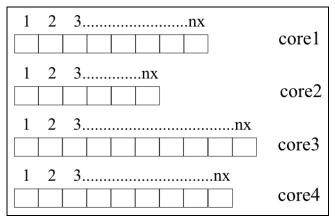

デバイスシミュレータと、プロセスシミュレー タの拡散計算部分の並列化を行った際に採用し た手法を以下に示す。まず、並列計算のために計 算領域の分割を行うと、分割した領域の端の部分 を各 CPU コアで保持し、計算中に相互にこの部 分の情報を通信を行い補完し合う必要が出て来 る。そこで、この重複部分の値を保持する1次元 配列を各 CPU コア上に用意し、計算中に必要な ときにこの配列から値を呼びだすようにした。こ こで、重複部分について一般的には、各 CPU コ アで大きさが異なるため、1次元配列のサイズも 各 CPU コアで異なる。また、この 1 次元配列の インデックスは、1から始まるようにしているた め、情報は本来の節点番号を失った形で保持され ることになる(図 56)。よって、重複部分のロー カルな番号と本来の節点の番号を結びつける情 報を保持する配列が必要となるため、これを用意 した。

図 56 各 CPU コアにおける重複部分の格納配列 のイメージ (4 コアの場合)

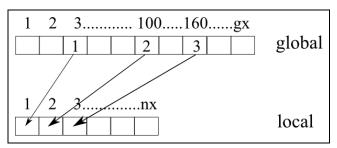

図 57 グローバルな節点番号とローカルな番号の関連づけ

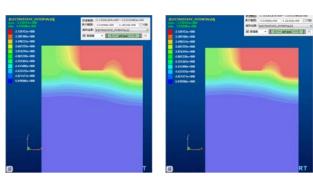

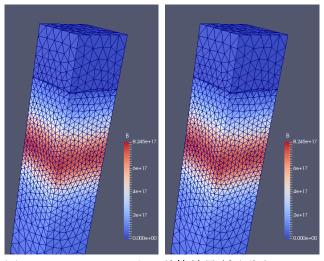

図 57 は、例として、計算中に節点番号3、100、 160 が必要なときにローカルな番号の配列の情報 を読みにいく仕組みを示している。まず、各 CPU コアが担当している領域に属する節点番号や計 算に必要のない節点番号の global 配列には"-1"な どの値を入れておき、それ以外の重複領域の節点 番号の global 配列にはローカルな番号を入れてお く。プログラム中で計算に必要な節点番号、かつ 各 CPU コアの担当外の節点番号が現れたら global 配列から節点番号の配列に格納されているロー カルな番号を取り出し、ローカル配列に格納され ている物理量を取り出す。このような仕組みを用 意することで、領域分割により必要となる重複領 域の情報の保持と計算中における値の取得をス ムーズに行うことを可能にしている。一方、行列 部分の計算については、デバイスシミュレータで は、行列ソルバーライブラリ PETSc[23]を採用し ており、プロセスシミュレータでは、行列ソルバ ーライブラリ Lis[24]を採用している。2 つのシミ ュレータで異なるライブラリを採用した背景に は、デバイスシミュレータにおける電流連続方程 式の並列計算時における収束性の問題が関係し ている。以下に、デバイスシミュレータ、プロセ スシミュレータ (拡散計算) における非並列計算 の結果と、並列計算の結果の比較を示す。まず、 デバイスシミュレータにおいては、例題として MOSFET についての計算を行い、得られたポテン シャル分布を図 58 に示している。左図は非並列 計算の結果を示し、右図は並列計算(4CPU コア) の結果を示している。どちらも同じカラーコンタ ーのレンジを用いて表示しており、全く同じ結果 が得られている。続いて、プロセスシミュレータ における不純物拡散計算の結果として得られた 不純物分布を図 59 に示している。左図は非並列 計算の結果を示し、右図は並列計算(4CPU コア) の結果を示しており、デバイスシミュレータの結 果と同様に全く同じ結果が得られている。以上よ り、上述した並列計算手法を用いて正しく結果が 得られることを確認した。

図 58 1CPU コアによる計算結果(左図) と 4CPU コアによる計算結果(右図)

図 59 1CPU コアによる計算結果(左図) と 4CPU コアによる計算結果 (右図)

# 7.2. 並列計算効率

デバイスシミュレータにおける並列計算時に、CPU コア数を増加させていくと電流連続方程式の行列計算の収束回数が著しく増加していき、並列計算の効率が悪化する問題に直面した。以下に、図 58 で示した MOSFET 計算の中で、一回行列を解くのに要する計算時間と収束回数(iteration)のCPU コア数依存性を、ポアソン方程式の求解時(表 2)、電流方程式の求解時(表 3)について示す。

表 2 ポアソン方程式ソルバーの CPU コア数に 対する計算時間と収束回数

| CPU コア数 | 計算時間[sec] | iteration |

|---------|-----------|-----------|

| 1       | 2.255657  | 42        |

| 2       | 2.044689  | 76        |

| 4       | 1.061839  | 74        |

| 8       | 0.642902  | 73        |

| 12      | 0.737887  | 94        |

表 3 電流連続方程式ソルバーの CPU コア数に 対する計算時間と収束回数

| CPU コア数 | 計算時間     | iteration |

|---------|----------|-----------|

| 1       | 44.68221 | 896       |

| 2       | 24.04335 | 997       |

| 4       | 12.42711 | 986       |

| 8       | 17.47534 | 2122      |

| 12      | 34.28479 | 4942      |

表 3 に示す通り、CPU コア数を増加させていくと、電流連続方程式の収束回数が極端に増加して計算の高速化を妨げている。この結果を踏まえ、非並列計算時の計算速度だけではなく、並列計算時には収束回数の増加をある程度抑え、計算効率が高くなる前処理と行列解法の調査、さらにパラメータ調整を行い得られた結果を以下に示す。

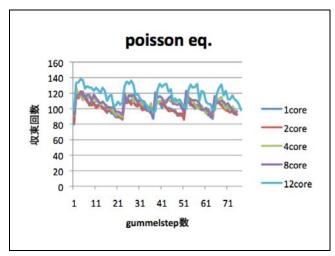

図 60 ポアソン方程式ソルバーの gummel step 数 に対する収束回数の CPU コア数依存性

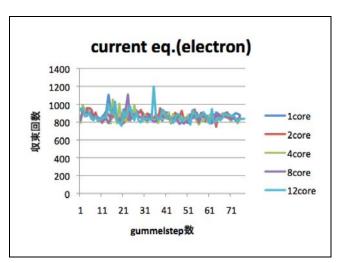

図 61 電流連続方程式ソルバーの gummel step 数 に対する収束回数の CPU コア数依存性

図 60、図 61 は、修正を行った後のポアソン方程式ソルバーと電流連続方程式ソルバーのgummel step 数に対する収束回数の CPU コア数依存性を示している。修正により、CPU コア数が増加しても収束回数の増加を抑えることに成功している。特に電流連続方程式ソルバーにおいて劇的な効果が得られている。

ここまでの作業を踏まえた上で、以下に示すテ スト例題を用いて並列化効率の評価を行う。

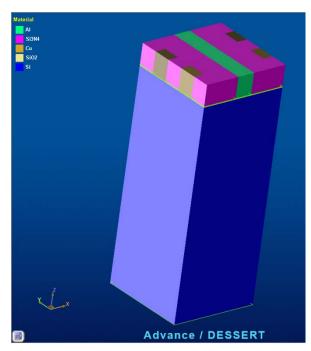

図 62 テスト例題に用いた CMOS 構造

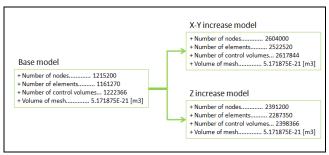

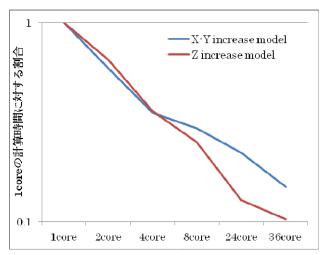

図 63 基本モデルとそこから作成した2つのモデル

評価に際して、基本となる節点数 100 万程度の モデルを用意し、そこから、並列計算時に最もデ ータ転送量が少なくなるように格子を分割した 250 万節点程度のモデル (z increase model) と、 最もデータデータ転送量が多くなるように格子 を分割した 250 万節点程度のモデル(x-y increase model)を作成し、2 つのモデルについて並列化効 率を取得した (図 64)。これにより、並列計算時 のデータ転送量による効率の違いを比較するこ とが可能となる。それぞれのモデルについて取得 した、非並列計算時(1CPU コア)での計算時間 と並列計算時の計算時間に対する割合の CPU コ ア数依存性を図 64 に示した。ここで、縦軸の値 の逆数が並列化効率を示している。結果は、4CPU コアを超えたあたりから並列化効率に違いが現 れ、z increase model の方が、x-y increase modell よ りも高い並列化効率が出ているものとなった。こ

の2つのモデルの差がデータ転送量の違いによる 並列化効率の差となっている。ここでは、36CPU コア使用時に、z increase model で約 10 倍、x-y increase model で約7倍の並列化効率となっている。

図 64 1CPU コアによる計算時間に対する使用 CPU コア数を増加させていった場合の計算時間 の割合 (両対数グラフ)

図 65 1CPU コアによる計算時間に対する使用 CPU コア数を増加させていった場合の計算時間 の割合 (両対数グラフ)

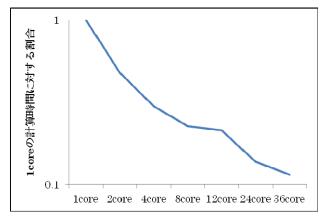

次に、プロセスシミュレータの拡散計算における並列化効率の取得について述べる。まず、データ取得のための計算は、図 59 に示したモデルで行った。プロセスシミュレータが使用している格子は、非構造格子の4面体となっているため、構造格子を採用しているデバイスシミュレータで用意したようなテスト例題を準備することは難しいため、1 つの例題についてのデータ取得を行っている。拡散 full model を用いて計算を行って

いるため、計算規模は16109要素×10方程式=160 万規模となっている。得られた結果を図 65 に示 す。

デバイスシミュレータと同様に、CPU コア数を 増やしていくと計算時間は短くなり、グラフの値 は小さくなっていく。8CPU コア使用時には約5 倍、36CPU コア使用時には約9倍の並列化効率が 得られている。

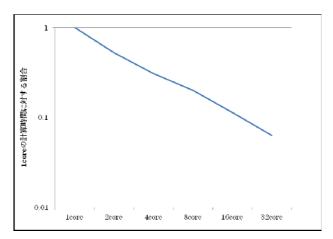

ここまでのデータ取得で使用した環境は弊社の PC クラスター環境となっており、データ通信速度は、本格的な並列計算システムと比較すると十分ではない可能性がある。そこで、海洋研究開発機構が所有する UV2000 において取得した並列化効率を以下に示す。これによると、図 64 に比べて高い並列化効率を少ない CPU コア数で実現していることが分かる。16CPU コアで約 9 倍32CPU コアで約 16 倍の並列化効率を達成している。この違いは、上述した使用環境におけるデータ通信速度が由来となっていると考えられる。

図 66 1CPU コアによる計算時間に対する使用 CPU コア数を増加させていった場合の計算時間 の割合(両対数グラフ): UV2000 におけるデータ

#### 7.3. まとめ

今回採用した並列計算手法と行列計算ライブラリを用いることにより、デバイスシミュレータにおいて 16CPU コア使用時に約 9 倍、32CPU コア使用時に約 16 倍、一方、プロセスシミュレータの不純物拡散計算において 8CPU コア使用時に約 5 倍、36CPU コア使用時に約 9 倍の並列化効率を得ることが可能であることを示した。この並列

化した TCAD プログラムを用いることにより、大 規模な TCAD 計算を手軽に実行可能とすること ができる。

# 8. ニュートン法による計算

# 8.1. はじめに

ポアソン方程式、電子電流連続式、正孔電流連 続式は変数が絡み合った非線形方程式であり、そ れぞれの式を線形化して反復的に解く必要があ る。

反復的に解く方法のうち、3 方程式をカップルさせて解く Newton 法はヤコビ行列の考え方に基づくもので、k 回目の反復値が解に近いときはTaylor 展開した式

$$\begin{pmatrix}

f_{1}(\psi_{k+1}, n_{k+1}, p_{k+1}) \\

f_{2}(\psi_{k+1}, n_{k+1}, p_{k+1}) \\

f_{3}(\psi_{k+1}, n_{k+1}, p_{k+1})

\end{pmatrix} = \begin{pmatrix}

f_{1}(\psi_{k}, n_{k}, p_{k}) \\

f_{2}(\psi_{k}, n_{k}, p_{k})

\end{pmatrix} + \begin{pmatrix}

df_{k1} / d\psi df_{k1} / dn df_{k1} / dp \\

df_{k2} / d\psi df_{k2} / dn df_{k2} / dp \\

df_{k3} / d\psi df_{k3} / dn df_{k3} / dp

\end{pmatrix} \begin{pmatrix}

\psi_{k+1} - \psi_{k} \\

n_{k+1} - n_{k} \\

p_{k+1} - p_{k}

\end{pmatrix} + \dots$$

(65)

に基づくもので  $(df_{ki} = f_i(\psi_k, n_k, p_k))$ 、1 次の項より、

$$\begin{pmatrix}

df_{k1}/d\psi & df_{k1}/dn & df_{k1}/dp \\

df_{k2}/d\psi & df_{k2}/dn & df_{k2}/dp \\

df_{k3}/d\psi & df_{k3}/dn & df_{k3}/dp

\end{pmatrix} \begin{pmatrix}

\delta\psi \\

\delta n \\

\delta p

\end{pmatrix} = -\begin{pmatrix}

f_{1}(\psi_{k}, n_{k}, p_{k}) \\

f_{2}(\psi_{k}, n_{k}, p_{k}) \\

f_{3}(\psi_{k}, n_{k}, p_{k})

\end{pmatrix}$$

(66)

を解くものである。

Gummel 法とも呼ばれる 3 組の方程式を逐次的に解く方法[2]に対して、それぞれの方程式のポテンシャルおよびキャリア密度の微分項を左辺の係数として作成する必要がある。Gummel による反復法では、

$$f(x) = Ax - b \tag{67}$$

のうち、bのみが右辺であったのが、

$$-f(x_{k}) = -(Ax_{k} - b)$$

(68)

が右辺に現れるため  $Ax_k$  を計算する必要がある。解に近づくと、右辺および解とも絶対値が小さくなる。 Gummel 法では、電極に接する節点では境界条件として固定値がb にはいるが、Newton 法では  $Ax_k$  に相殺されて 0 に近づく形になる。

Gummel 法は創始者が Gummel であるが、 Newton 法は多くの分野でも一般的に用いられており、デバイスシミュレーションが始まった比較的初期から用いられていたため、デバイスシミュレーションの式に誰が初めに用いたかは不詳であるが、現在 Gummel 法も Newton 法の両方が共存して用いられている。

# 8.2. ポアソン方程式での離散式

ポアソン方程式

$$-\nabla \cdot (\varepsilon_s \nabla \psi) = \frac{q}{\varepsilon_0} (-n + p + N_D - N_A)$$

(69)

は、深い準位を考えない場合。

$$-\nabla \cdot (\varepsilon_{s} \nabla \delta \psi) + \frac{q}{\varepsilon_{0}} \delta n - \frac{q}{\varepsilon_{0}} \delta p =$$

$$\nabla \cdot (\varepsilon_{s} \nabla \psi) + \frac{q}{\varepsilon_{0}} (-n + p + N_{D} - N_{A})$$

(70)

となる。ポテンシャルは Gummel 法での Gummel 項を除いた係数が流用できる。

キャリア密度は差分式のうち対角成分の係数の みが現れる。

トラップ準位を考慮した場合、Fermi 統計による縮退を考える場合、キャリア密度に依存した補 正項が加わる形で実装されているが、本報では詳 細は省略する。

# 8.3. 電流連続式での離散式

電子、正孔の濃度および電流密度をそれぞれ n, p および Jn、Jp とすると、式(27)、(28)の電流連続方程式が成り立つ。

また R、G は、それぞれ再結合・生成率である。 ドリフト拡散モデルの場合、電流密度はドリフト 成分と拡散成分の和で表わされる。

$$J_n = -qn\mu_n \nabla \psi + qD_n \nabla n \tag{71}$$

$$J_{p} = -qp\mu_{p}\nabla\psi - qD_{p}\nabla p \tag{72}$$

ここで、 $D_n$ 、 $D_p$  および  $\mu_n$ 、 $\mu_p$ はそれぞれ電子 と正孔に対する拡散係数と移動度である。

式(27)、(28)に式(71)、(72)を代入すると

$$\frac{\partial n}{\partial t} = \nabla \cdot (-n\mu_n \nabla \psi + D_n \nabla n) - R + G \tag{73}$$

$$\frac{\partial p}{\partial t} = \nabla \cdot (p\mu_p \nabla \psi + D_p \nabla n) - R + G \tag{74}$$

式(73)の $(-n\mu_n\nabla\psi+D_n\nabla n)$ の項について Scharfetter-Gummel の方法[25]により Bernoulli 関数を導入して差分が表現されている。

$$\frac{k_B T}{q} \frac{A_{ij}}{d_{ij}} (\frac{\mu_{n,i} + \mu_{n,j}}{2}) (B(U_{ij}) n_i - B(U_{ji}) n_j)$$

(75)

$$B(x) = \frac{x}{e^x - 1} \tag{76}$$

$$U_{ij} = \frac{q}{k_B T} \left[ (\psi_i + \delta \psi_{QM,i} + \delta \psi_{Fermi,n,i}) - (\psi_j + \delta \psi_{QM,j} + \delta \psi_{Fermi,n,j}) \right]$$

(77)

ただし、量子補正モデルの項 $\delta\psi_{QM}$ 、Fermi 統計の項 $\delta\psi_{Fermi,n}$ はユーザーが選択した場合のみはいる。Advance/TCAD の量子補正モデルの項は、界面での障壁高さと位置から決まりポテンシャルやキャリア密度の関数ではない。

# 8.4. GR 項での離散式

微分項の導出は可能なものは微分するが、電界密度や電流密度のように微分が非常に複雑なものはしない。すなわち、移動度、インパクトイオン化項は微分しないものを実装してある。この場合、電界密度や電流密度の微分がないため、差分式のうち当該節点の対角ブロック行列要素のみに加わる。本報では詳細は省略する。

# 8.5. 例題適用

Newton 法は、一度に3組の方程式を解くため、 反復回数は一般に減るが、Gummel 法の反復1回 当たりの計算時間が長くかつメモリを多く要す る。そのため Gummel 法で安定に解ける場合は有 利といえない。

Newton 法が有利なのは、高注入状態である。高 注入状態では、ポテンシャルとキャリア密度のカ ップリングが強く別々に解くと解が振動する場 合がある。特にダイオードの順方向特性で効果が あることを確認した。また MOSFET のオン電流 計算でも、Newton 法が速い場合が多い。

一方電流が低い逆方向特性で Gummel 反復法の 収束が悪い例題に関しては、Newton 法は必ずしも 有利ではなく例題によって速かったり遅かった りする。そのため、市販シミュレータでも Gummel 法と Newton 法の選択はユーザーに委ねており、 Advance/TCAD でも同様にユーザーの選択に委ね る形にしている。

# 参考文献

- [1] D. E. McCumber and A. G. Chynoweth, "Theory of negative-conductance amplification and of Gunn instabilities in "two-valley" semiconductors" IEEE Transactions on Electron Devices, vol.:ED-13, no. 1, pp. 4 21, 1966

- [2] H. K. Gummel, "A self-consistent iterative scheme for one-dimensional steady state transistor calculations" IEEE Trans. Electron Devices, vol. ED-11, no. 10, pp. 455 – 465, 1964

- [3] D. Vandope, "An accurate two-dimensional numerical analysis of the MOS transistor", Solid State Electron., vol. 15, pp. 547 557, 1972

- [4] D. P. Kennedy and P. C. Murley, "Steady state mathematical theory for the insulated gate field effect transistor", IBM J. Res. Develop., vol. 17, pp. 2- 12, 1973

- [5] M. S. Mock, "A two-dimensional mathematical model of the insulated-gate field-effect transistor", Solid State Electron., vol. 16, pp. 601 – 609, 1973

- [6] R.W. Hockney; R.A. Warriner; and M. Reiser, "Two-dimensional particle models in semiconductor-device analysis", Electronics Letters, Volume 10, Issue 23, 14 November 1974, pp.. 484 – 486

- [7] 山口 憲、冨澤 一隆、"非平衡電子輸送論", アドバンスソフト出版事業部

- [8] W. Shockley and W. T. Read, "Statistics of recombinations of holes and electrons", Phys. Rev., vol. 87, no. 5, pp. 835-842, Sept. 1952

- [9] R. N. Hall, "Electron-hole recombination in germanium", Phys. Rev., vol. 87, p. 387, July 1952

- [10] E. J. Mcgrath and D. H Navon, "Factors limiting current gain in power transistors", IEEE Trans. Electron devices, vol. ED-24, no. 10, pp. 1255 – 1259, 1977

- [11] http://physics.nist.gov/PhysRefData/Star/Text/AS TAR.html

- [12] K. Yamaguchi, "Field-Dependent Mobility Model for Two-Dimensional Numerical Analysis of MOSFET's", IEEE Trans. Electron Devices, vol. ED-26, no. 7, pp. 1068 - 1074, July 1979

- [13] K. K. Thornber, "Relation of drift velocity to low-field mobility and high-field saturation velocity," J. Appl. phys., vol. 51, no. 4, pp. 2127-2136, Apr. 1980

- [14] K. Yamaguchi, S. Sakurai and K. Tomizawa, "An accurate and simplified modeling of energy and momentum relaxation rates for metal-oxidesemiconductor device simulation", Japan. J. Appl. Phys., vol. 49, (2010) 024303

- [15] 山口、桑原、小池、"次世代 TCAD (4) 準バリスティックモデルの高精度・高速計算法" 第60 回応用物理学会春季学術講演会、講演番号28p-G7-4、2013 年 3 月 28 日 神奈川工科大学、2013 年(平成 25 年)春季

- [16] 山口 憲、"パワーデバイス用シミュレータの 技術課題" アドバンスシミュレーション、vol. 8, pp. 59 - 66, 2011

- [17] A. Schenk and U. Krumbein, "Coupled

- defectlevel recombination: Theory and application to anomalous diode characteristics" J. Appl. phys., vol. 78, pp. 3185 3192, 1995

- [18] K. Yamaguchi, T. Kuwabara, and T. Uda, "A generation/recombination model assisted with two trap centers in wide band-gap semiconductors" J. Appl. Phys, 113, 104506 (2013)

- [19] G. E. Moore. Electronics, "Cramming more components onto integrated circuits", Electronics, Vol. 38, No. 8. (19 April 1965), pp. 114-117

- [20] J. Gregory Rollins and John Choma, Jr., "Mixed-Mode PISCES-SPICE Coupled Circuit and Device Solver", IEEE Trans. Computer-Aided Design, vol. 7, no. 8, pp. 862 -867, August 1988

- [21] Y. Takemura, K. Osada, M, Yagyu, K. Yamaguchi, J. Ushio and T. Maruizumi, "Three-dimensional capacitance analysis in an SRAM cell", 2000 International Conference on Solid State Devices and Materials, August 380 - 381, 2000, Sendai, Japan

- [22] Y. Takemura, K. Osada, M, Yagyu, K. Yamaguchi, J. Ushio and T. Maruizumi, "Three-dimensional effects obtained from capacitance analysis of an SRAM cell", Technical Proc. Of the 4th Int. Conf. On Modeling and Simulation of Microsystems (MSM2001), p. 394, SC., USA

- [23] http://www.mcs.anl.gov/petsc/

- [24] http://www.ssisc.org/lis/

- [25] D. L. Scharfetter and H. K. Gummel, "Large signal analysis of a silicon Read diode," IEEE Trans. Electron. Dev., vol. 16, pp. 64–77 (1969).

- ※ 技術情報誌アドバンスシミュレーションは、 アドバンスソフト株式会社 ホームページのシ ミュレーション図書館から、PDF ファイル (カ ラー版) がダウンロードできます。ダウンロー ドしていただくには、アドバンス/シミュレー ションフォーラム会員登録が必要です。