# 速報「Xeon Phi による第一原理計算の高速化」 西原 慧径\*

## "Xeon Phi can accelerate First-Principles calculation"

Satomichi Nishihara\*

2013年1月、Intel 社より Xeon Phi<sup>†</sup>コプロセッサーの販売が開始され、CPU や GPU に代わる新しいアーキテクチャとして、科学技術計算への応用が期待されている。そこで、弊社では第一原理計算ソフトウェア「Advance/PHASE Ver. 3.2」を Xeon Phi に対応させ、計算の高速化を試みた。本稿では、プログラムの実装方法および簡単なベンチマーク結果を紹介する。

Key word: First-Principles calculation, Density functional theory, Advance/PHASE, Xeon Phi, Coprocessor, MIC

#### 1. はじめに

近年、ハイパフォーマンス・コンピューティングの分野において、GPU やコプロセッサー等の補助デバイスによる数値計算の高速化が盛んに試みられている。現在のスーパーコンピュータTOP500においても、補助デバイスを搭載したマシンが数多く見受けられる。弊社においても、この流行を取り入れて、より高度なサービスを提供すべく製品開発に取り組んでいる。

その第一弾として、弊社の第一原理計算ソフトウェアである Advance/PHASE Ver.3.2 のソースコードの一部を、Intel 社のコプロセッサーである Xeon Phi に対応させた。修正したソースコードは、CPU 1 コアの 20 倍以上に高速化されることが確認された。以降の章にて、詳細な内容を紹介する。

#### 2. Xeon Phi について

Xeon Phi は PCI Express 形式の拡張カードとして提供されており、外観はハイエンドな GPU に似ている。利用方法も GPU と同様に単独では機能せず、プロセッサーの処理を補助するデバイ

\*アドバンスソフト株式会社 第1事業部 1st Computational Science and Engineering Group, AdvanceSoft Corporation

<sup>†</sup>Xeon Phi は、アメリカ合衆国およびその他の国 における Intel 社の登録商標です。 スである。そのため、Intel 社は「コプロセッサー」と呼称している。

ハードウェアの最大の特徴は、動作クロックが約1GHzのコアを60個程度搭載していることである。利用可能なハイパースレッドは、約240である。倍精度浮動小数点演算性能の理論値は約1TFLOPSであり、単位消費電力量当たりの性能が一般的なCPUよりも優れている(Xeon Phiの消費電力量は約300Wである)。また、6~16 GBのメモリーが搭載されており、種々の事案に対する汎用的な利用が可能である。

ソフトウェアの特徴としては、コアが x86 互換であり、CPU 用に開発されたソースコードがそのまま利用可能なことである。OpenCL や CUDA等の専用言語を使用する GPU に対して、優位な点である。また、Xeon Phi 自体に Linux OS が搭載されており、SSH にてログインできる。プログラムの実行方式には、Xeon Phi にログインして直接実行する「ネイティブ実行」と、CPU から処理の一部をポストする「オフロード実行」がある(詳細は、Intel 社ホームページ[1]を参照のこと)。比較的大規模なソフトウェアの場合にはメモリーを多く使用するため、ネイティブ実行よりもオフロード実行の方が適している。

## 3. Advance/PHASE Ver. 3.2 の高速化

Advance/PHASE Ver. 3.2 を Xeon Phi にて実行し、計算の高速化を試みた。第一原理計算では、多くのメモリーを使用するため、オフロード実行を適用した。オフロード実行の場合、ソースコードの一部に修正が必要である。ソースコードの修正内容、およびベンチマーク計算の結果を以下に記す。

#### 3.1. ソースコードの改修

本来 Xeon Phi でプログラムを実行する場合、CPU 用のソースコードを修正せずに、そのまま利用できる。しかしながら、オフロード実行の場合、処理の一部分のみを Xeon Phi にて実行するため、Xeon Phi で実行する箇所を指定する必要がある(C 言語の#pragma、Fortran の\$DIR にて指定する)。本対応にて修正を施したのは、SCF計算のボトルネックの一部である、(i)射影演算子  $|oldsymbol{\beta}\rangle$ と波動関数  $|oldsymbol{\psi}\rangle$ の内積演算

$$\langle \beta | \psi \rangle$$

(1)

および、(ii)非局所ポテンシャル $V_{NL}$ と波動関数 $|\psi

angle$ の積演算

$$V_{NL} | \psi \rangle$$

(2)

である。

(i),(ii)の計算において、CPU用のソースコードは Level3-BLAS[2]を含んでおり、この処理が最も計算時間を要する。そこで、ソースコードに以下の修正を施して、計算の並列化・高速化を試みた。

- ① Level3-BLAS の計算に、Xeon Phi 上で動作する並列化された MKL[1]を適用した。

- ② Level3-BLAS の呼び出し回数を可能な限り少なく、行列サイズを可能な限り大きくした。行列サイズが大きくなると MKL の実行効率が向上する。

- ③ 行列要素は直接に Xeon Phi に転送せず、 必要最小限のデータのみを転送して Xeon Phi 上にて行列要素を作成する。行列要素 の作成処理は OpenMP にて並列化した。

つまり、予め最適化されたライブラリー(MKL)を 利用して、少ない開発コストで確実に高速化され る方法を採用している。また、行列要素を Xeon Phi 上で作成することで、CPU と Xeon Phi との 間の通信量を少なく抑えている。

## 3.2. ベンチマーク計算

## ① 計算

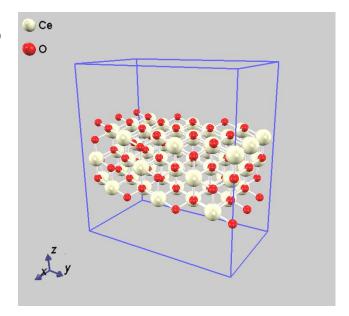

ベンチマーク計算に使用した系は、 $CeO_2$ のスラブである(図 1)。GGA 交換相関汎関数およびウルトラソフト擬ポテンシャルを使用して、Kohn-Sham 密度汎関数法[3]の計算を実施した。ただし、SCF 計算の 1 サイクルのみを実行して、計算時間の測定を行った。系の原子数は 162、k 点の数は 4、波動関数を展開する平面波の数は 60313、バンド数は 1014、射影演算子の数は 2052 である。

計算に使用したコプロセッサーは、Intel 社の Xeon Phi 5110P(60 コア, 240 スレッド)1 基で ある。また、計算時間の比較のため、CPU(Xeon X5660(6 コア))にて同様の計算を実施した。

図 1 CeO<sub>2</sub>のスラブ

## ② 結果

Xeon Phi のスレッド数を種々の値として、 $\left\langle eta \middle| \psi \right

angle$  および  $\left. V_{\scriptscriptstyle NL} \middle| \psi \right

angle$ の計算時間をそれぞれ表

1 および 2 に示す。 CPU の計算時間は 1 コア当 たりの値である。また、環境変数

MIC\_KMP\_AFFINITY は balanced とした。

$\langle \beta | \psi \rangle$  および  $V_{NL} | \psi \rangle$ のいずれの場合においても 240 スレッドの場合が最も計算速度が速く、物理コア数(60)を上回るハイパースレッドの有用性が確認された。 240 スレッドの時の Xeon Phiの計算時間は、 $\langle \beta | \psi \rangle$ の計算では CPU 1 コアの 1/24.6、 $V_{NL} | \psi \rangle$ の計算では CPU 1 コアの 1/24.6、 $V_{NL} | \psi \rangle$ の計算では CPU 1 コアの 1/24.6、大幅な高速化が確認された。

表 1  $\langle \beta | \psi \rangle$ の計算時間

| /        |            |

|----------|------------|

| スレッド数    | 計算時間 / sec |

| 10       | 266.9      |

| 20       | 130.4      |

| 30       | 104.1      |

| 40       | 86.1       |

| 60       | 70.7       |

| 80       | 54.8       |

| 120      | 52.2       |

| 240      | 45.6       |

| CPU      | 1123.5     |

| (1コア当たり) | 1120.0     |

表 2  $V_{\scriptscriptstyle NL} |\psi\rangle$ の計算時間

| スレッド数    | 計算時間 / sec |

|----------|------------|

| 10       | 365.2      |

| 20       | 159.5      |

| 30       | 122.1      |

| 40       | 90.5       |

| 60       | 70.4       |

| 80       | 55.8       |

| 120      | 49.0       |

| 240      | 36.7       |

| CPU      | 832.3      |

| (1コア当たり) | <u></u>    |

## 4. まとめ

Xeon Phi により、第一原理計算のボトルネックが高速化されることが確認された。CPU 1 コアの 20 倍以上の高速化であり、コプロセッサー1枚で CPU 3~4 枚分の演算性能である。Xeon Phi の価格を鑑みれば、極めて良いコストパフォーマンスであり、今後の普及が期待される。弊社においても製品開発を継続し、Advance/PHASE Xeon Phi 対応版をリリースする予定である。

#### 5. 謝辞

本稿で紹介したベンチマーク計算において、 Xeon Phi コプロセッサーの計算には株式会社コンカレントシステムズ[4]の計算サーバを使用させていただきました。関係者各位に深く感謝申し上げます。

## 参考文献

- [1] http://software.intel.com/en-us/mic-develop er

- [2] http://www.netlib.org/blas/

- [3] W. Kohn, L. J. Sham, *Phys. Rev.* **1965**, *140*, A1133

- [4] http://www.concurrent.co.jp/

※技術情報誌アドバンスシミュレーションは、アドバンスソフト株式会社 ホームページのシミュレーション図書館から、【カラー版】がダウンロードできます。(ダウンロードしていただくには、アドバンス/シミュレーションフォーラム会員登録が必要です。)