## パワーデバイス用シミュレータの技術課題 山口 憲\*

# Device simulation technology for high power applications Ken Yamaguchi\*

#### 1. はじめに

未曾有の大震災とそれに伴い発生した電力危機は日本人のみならず世界中の人々に、人類の持続的発展とエネルギー資源の活用問題に関して大きな警鐘を鳴らした。省エネは人類に必要不可欠な課題であり、現実的には電力用機器を始め電気応用部品の高効率化が強く望まれる。本稿では電気機器の内、近年、需要が拡大しているハイパワー応用半導体デバイスに焦点を絞り、設計に必要なデバイスシミュレーション技術について考察を進めてみたい。

#### 2. デバイスシミュレーションの技術課題

半導体デバイスは微細化の一途にあることは周知の事実である。超高密度、高性能 LSI は今日の高度情報化社会の基盤インフラであり、家庭用の電気製品に至るまで、広く使われている。超微細・高密度実装 LSI 設計には微細化に伴う形状ゆらぎや不純物濃度の統計的バラツキに代表される「非一様性」に対するマージン設計、デバイス動作の面からは微細化に伴うバリスティック効果の有効活用等が設計課題となる。

これに対し、ハイパワー応用を考えるとデバイス 設計技術に課せられる課題は

- 1) 高電圧計算機能、降伏電圧解析機能

- 2) エッジブレークダウンを回避するための円形パターンの採用と3次元解析

- 3) ワイドギャップ半導体の導入に伴う真性キャリア密度の急激な減少と数値計算精度の確保

- 4) ガードリングに見られる浮遊電位問題

- 5) 発熱、放熱解析

\*アドバンスソフト株式会社 総合企画部 General Planning Division, AdvanceSoft Corporation などがパワーデバイス特有の項目として列挙される。項番 5)の熱放散問題は 3 次元解析が必要である。項番 2)の 3 次元効果解析機能と共通し、かつ、超微細構造 LSI 設計における「非一様性」、「バラツキ」問題で必須となる 3 次元解析とも共通の課題であるので、本稿ではパワーデバイス固有課題として、項番 1), 3), 4)を中心に考えていく。

## 3. デバイスシミュレーションの方法論

#### 3.1. 基本方程式

パワー用半導体デバイスは高密度実装という面からは最新の LSI と同様であるが、デバイス単体で見れば必ずしも超微細構造ではない。つまり、バリスティック輸送モデルまで考慮する必要性は低い。従って、デバイスシミュレーションに必要なモデリングとしては古典的ドリフト拡散(Drift- Diffusion: DD)モデルが基本となる。ここで改めて DD モデルを電子電流(Jn)、正孔電流(Jp)の各成分について記述すると

$$\nabla \boldsymbol{J}_{n} = R - G \tag{1}$$

$$\nabla \boldsymbol{J}_{p} = G - R \tag{2}$$

となる。電流密度ベクトルの成分は

$$\boldsymbol{J}_{n} = n\mu_{n} + D_{n}\nabla n \tag{3}$$

$$\boldsymbol{J}_{p} = p\mu_{p} - D_{p}\nabla p \tag{4}$$

である。これらに電位・電界分布を与える Poisson 方程式

$$\varepsilon \nabla^2 \Psi = -q(N_D - N_A - n + p) \tag{5}$$

を加え、上式群に対する self-consistent な解を求めることで、電子/正孔/電位(電界)分布を詳細に知ることが可能となる。なお、ここに No, Naはドナー型、アクセプター型の不純物濃度を表す。

最後に、以降の定量的議論を明確にするため生

成・消滅(再結合)項(GR項)を記述しておく。 a)消滅項

$$R = R_{SRH} + R_{sp} + R_{Aug} \tag{6}$$

右辺第1項は一準位を介した間接型再結合、第2項 は直接再結合、第3項はオージェ型再結合を表す。 通常動作では第1項が主要因となる。

#### b) 生成項

パワー応用デバイスではアバランシェ増倍機構 が最も大きな降伏要因であり、

$$G = \alpha_n |\boldsymbol{J}_n| + \alpha_p |\boldsymbol{J}_p| \tag{7}$$

とモデル化されている。係数 $\alpha$ はイオン化率と呼ばれ、電界強度(E)に対し

$$\alpha = A \times exp \left[ -\left(\frac{E_0}{E}\right)^{\gamma} \right] \tag{8}$$

のような依存性で近似される。指数 $\gamma$  はシリコンでは1 で近似される。

#### 3.2. 数値計算の方法

式(3),(4)をそれぞれ式(1),(2)へ代入すれば電流連続と呼ばれる2階の偏微分方程式が形成される。電流連続の式を安定に解くため表1のような幾つかの方法論が知られている。

表 1 数値計算法の種類

| 項番 | 方法名         |

|----|-------------|

| 1  | 流れ関数法       |

| 2  | 擬フェルミの指数関数法 |

| 3  | 擬フェルミ法      |

| 4  | キャリア密度法     |

項番 1 の流れ関数法[1]は流東ベクトルに対するベクトルポテンシャルを被解析関数とするもので、2 次元問題で、かつ、*GR*項がない時、強安定な数値解析手段となる。1970 年代、MOFSET の 2 次元解析とデバイス設計ツールとして活用された歴史がある。しかし、パワー用デバイス設計ではダイオード特性解析、降伏解析が要求されるため、さらに3 次元解析への拡張性を考えた時、流れ関数法が有

利とは言い難くなる。

項番 2 の擬フェルミポテンシャルの指数関数法 はダイオード解析に強力な手法である[2]。順・逆方 向特性解析に高精度計算が期待できる。しかし、指 数関数を用いるため、被解析関数の値の変域が大き くなる。このため、高電圧計算ではマシンオーバフ ロー・アンダーフローが起こり、高電圧解析への適 用が難しい。

項番3で述べた擬フェルミポテンシャルを被解析対象変数とする方法は高電圧計算に最も自然な関数形といえる。但し、ドリフト項に対し非線形が現れ[3]、数値計算上の安定収束と精度にトレードオフがでる。

最後の手法は被解析関数をキャリア密度 (n, p) [4]とするもので、値の変域が大きいことは項番 2 と同じであるが、変域幅は電圧に依存しない。この特質は高電圧解析に有利である。電流積分法を用いることで高精度な離散化が可能[5]である。しかし、キャリア密度の変域幅がバンドギャップに依存するため、ワイドギャップ系の材料には計算精度上に課題が残る。

いずれの手法も一長一短である。トータルで損得を考慮した時、本稿では項番4の手法を採用し、ハイパワー応用における技術課題を考えていく。

# 4. デバイスシミュレーションの解析例

#### 4.1. バンドギャップ依存性

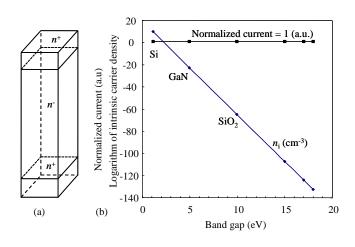

半導体中のキャリア密度に関しnp積一定の法則 (但し、中性領域内)がある。 $np = n_i^2$ の関係から、また真性キャリア密度 $n_i$ は図 1(b)に示される如くギャップ幅に対し指数関数的に小さくなることから、ワイドギャップ半導体ではn,p値の変域が大きくなる。しかし、電流密度の式[式(3),(4)]をみて分かるように、電流値にバンドギャプ依存項はない。表 1 項番 4 の手法を採用した場合の計算精度について、まず始めに、バンドギャップと電流値の関係を評価してみる。ここでは図 1(a)に示すような 1 次元単純バー構造を評価対象とした。キャリア密度法を採用した場合、同図(b)に示される如く、電流値の計算結果はバンドギャップに依存しない。なお図

(b)では、バンドギャップの大きさにおける代表的半導体材料を記載してある。評価範囲が Si から絶縁体(SiO2)までを網羅しており、半導体デバイス開発で必要な領域を評価していることが分かる。これより、ワイドギャップ半導体の解析にキャリア密度法を利用できることが理解できる。

図 1 バンドギャップと電気的特性 (a) 評価対象構造 (b) バンドギャップに対する 真性キャリア密度と構造(a)における電流値

### 4.2. ダイオードの逆方向耐圧解析 4.2.1. Si ダイオード

単純バー構造からダイオード構造へと評価対象を広げていく。ダイオードの逆方向飽和電流、いわゆる暗電流は式(1)、(2)に示される電流連続式の右辺の体積分により決められる。再結合項Rが非零となるのは空乏層内なので、実質、空乏層内のRの大きさが支配パラメータである。降伏電圧を決める生成項は逆方向飽和電流(暗電流)を種にして、式(7)で与えられるG項により表現できる。

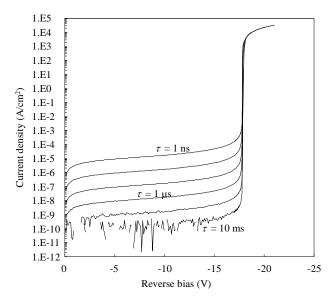

標準的例題としてシリコンを取り上げ、逆方向電流を解析してみる。計算結果を図 2 に示す。図では RSRH の大きさを決める主要因であるライフタイム(τ)をパラメータとして表現している。逆方向飽和電流の大きさがライフタイムに逆比例していることが分る。一つ問題となることはライフタイムが長く飽和電流レベルが低い領域での計算精度である。図から分かるように極低レベルでは計算精度を十分得ることができていない。これはプログラムが倍精度でコンパイルされているため、極微小電流の

計算精度が十分でないことを意味している。但し、 雪崩増倍による降伏特性は電界強度で決定され、ライフタイムに依存しない。つまりライフタイムを変 更しても降伏電圧は同じである。従って、ライフタイム $(\tau)$ が長い場合に起る電流値の減少は、雪崩増 倍による降伏電圧解析に影響を与えない。

図 2 Si ダイオードにおける逆方向特性解析

#### 4.2.2. SiC ダイオード

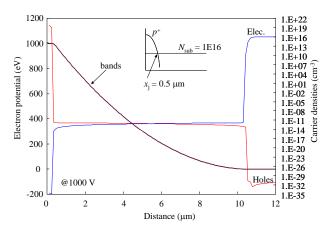

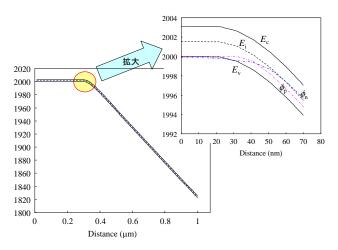

ハイパワー応用の観点からワイドギャップ半導体である SiC ダイオードの解析を進めてみる。まず数値計算能力を評価する目的で雪崩増倍項を数値モデルから外し、SRH 型再結合項のみ考慮したモデルでダイオード逆方向特性を計算する。図 3 は逆バイアス 1,000 V におけるバンド構造とキャリア密度を図示したものである。さらに 2,000 V まで逆バイアスした時のバンド構造と pn 接合付近での拡大図を図 4 に示す。図 3 のキャリア分布をみると10<sup>20</sup> から 10<sup>-30</sup> cm<sup>-3</sup> まで約 50 桁にわたる計算を行っていることが分る。高電圧計算は数千ボルトまで容易に実行できることを確認しており、キャリア密度法が高電圧計算に対し丈夫な計算手法(数値計算のタフネス)であることが分る。

一方、n領域における正孔分布(図 3 右端)の微小領域をみると、分布形状に不自然な曲線が見られる。 倍精度コンパイルで約 50 桁にわたる数値計算を行うことの限界が覗える。といっても、10 のマ

イナス 30 乗の大きさであり、実用上、影響のない 範囲である。

図 3 SiC ダイオードの逆バイアス解析

図 4 2,000 V 逆バイアスにおけるバンド構造

次に降伏特性を計算してみる。図 3,図 4の計算条件とは異なり、式(7)で表現される雪崩増倍効果を加えて解析を実行する。SiC ではバンドギャップが3 eV に及ぶため、真性キャリア密度が Si のそれより約 30 数桁小さくなる。この為、SRH 型再結合による暗電流も Si のそれと比べ、約 30 桁小さくなる。既に述べたように、倍精度コンパイルでは数値計算精度の確保が困難となる。この為、雪崩増倍機構の種電流を数値計算上、SRH 型再結合電流から計算できなくなる。

一方、SiC における雪崩降伏はイオン化係数の大きさから、電界強度が数 MV/cm の領域となる。この様な強電界領域では Zener 型[6]のバンド間トンネルが起こり得る。トンネル確率については Kane [7]による詳しい解析がある。トンネル電流をデバイ

スシミュレーションで計算するには GR 項へ組入れるモデルが便利である。本稿では  $Hurks\ et\ al\ [8]$ によりモデル化された下記 GR 項

$$G_{bbt} = A|F|^{\sigma} D(F, E, E_{fn}, E_{fp}) exp(-\frac{B}{|F|})$$

(9)

を用いる。ここにFが電界強度で、エネルギーEと識別するため特別に用いている。係数にあるDは伝導帯から価電子帯、価電子帯から伝導帯へトンネルする確率の差として表現される実効的トンネル効率で、デバイスシミュレーションに使い易い形式として

$$D = \frac{1}{\exp\left[\frac{q(\varphi_n - \Psi_i)}{k_p T}\right] + 1} - \frac{1}{\exp\left[\frac{q(\varphi_p - \Psi_i)}{k_p T}\right] + 1}$$

(10)

とモデル化できる。係数 Bはバンドギャップの関数となる。

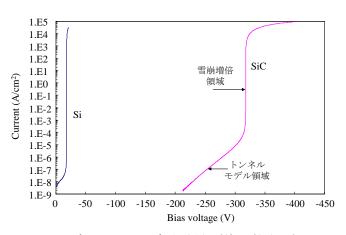

式(10)に示される Dの値は冶金学的接合付近で 1、それ以外の空乏層および中性領域では零となる。式 (9)から分かるように  $G_{obt}$ の値は電界に対し急峻な依存性を持っているので、式(9)が実質的に値をもつのは pn 接合の内、冶金学的接合付近である。つまり、式(9)の計算は、式(10)を乗算しなくとも、実質的に同等であることが容易に推測される。そこで、D=1 とおいた簡易モデルでトンネル電流を計算してみる。計算結果を  $S_{i}$  と対比させ、逆方向電流を片対数表現し、図 5 に示す。但し、 $S_{i}$  ダイオードの解析では  $G_{obt}$  を除外し、雪崩増倍効果のみを生成項として扱っている。

図 5 に見られる如く SiC ダイオード解析ではトンネルモデル( $G_{bbt}$ )と雪崩増倍モデルを組合せることで、トンネル電流とこれが種となって急峻な立ち上りを見せる雪崩増倍の発生を模擬できる。

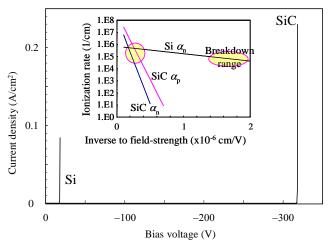

図 5 の縦軸を対数から線形表示に直すと、ダイオードの逆方向降伏特性として図 6 のような出力を得ることができる。雪崩増倍機構の元になるイオン化率は挿入図に示す如く Si と SiC では約一桁大きさが異なるため、降伏電圧も Si と SiC ダイオードでは約一桁大きさが異なっていることも定量的に示される。

SiC ダイオードの逆方向特性解析に式(9)に示す

ようなバンド間トンネルモデルを導入した。モデルの妥当性(電界強度依存性や係数の大きさ)については今後検討を要する。

図 5 ダイオードの降伏特性(片対数表示)

図 6 ダイオードの降伏特性(線形表示)

#### 4.3. 浮遊電極構造の解析

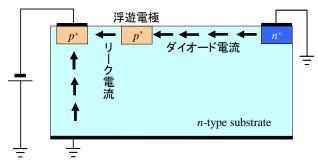

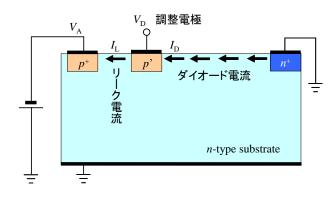

ハイパワー応用デバイスでは高耐圧化の為、ガードリングがシバシバ使用される。電界集中を抑えるためp領域の中にn領域、逆にn領域の中にp領域(図 7参照)を、電位を与える電極を持たせず埋め込む構造である。高濃度領域にも関わらず浮遊電位の領域が出現するため、数値計算が不安定になり易い。

浮遊電位は図 7 の場合、 $p^+-n-p'$ 構造に流れるリーク電流と、p'とn 領域間に流れるダイオード逆方向電流による IR ドロップから決まる。数値計算上の課題はダイオード暗電流の計算精度である。Si ダイオードの場合ライフタイムは通常 1  $\mu s$  程度であるから、図 2 に示されるように暗電流計

算における数値計算精度の確保は倍精度コンパイルでも可能である。

図 7 ガードリング付きダイオード構造 (浮遊電位の p 領域を持つダイオード)

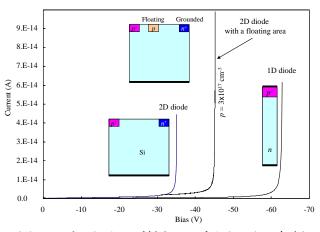

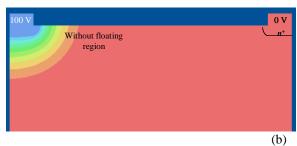

Si ダイオード浮遊電位領域付き構造における逆 方向降伏特性の計算例を図 8 に示す。倍精度計算 によるで、n 基板に p'領域を浮遊電位のまま設定し たものである。定量的妥当性を確認する目的で 1 次 元構造と浮遊電位領域を持たない 2 次元構造ダイ オードの計算例を併せて載せてある。1 次元構造の 耐圧が最も高く、逆に、浮遊電極構造を持たない 2 次元構造ではエッジ降伏から耐圧が最も低下して いる。浮遊電位構造とすることで、2 次元構造での 電界集中の緩和効果をもたらしていることが分か る。

図 8 ガードリング付き Si ダイオードの解析

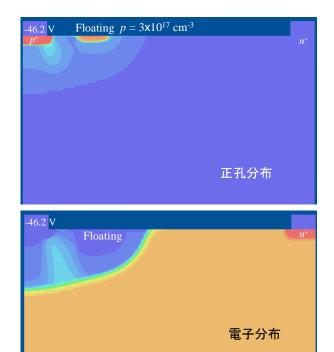

デバイス内部のキャリア分布を調べてみる。図 9 は降伏電圧付近における正孔 (上段)・電子分布 (下段) を示したもので、 $p^+$ 電極から n 基板へのキャリアリークが明瞭に示されている。なお、正孔分布図からは必ずしも明瞭ではないが、 $p^+$ 電極とp'領

域の間でも表面に沿ってキャリアリークが発生する。キャリアリークによる電流はデバイス内に *IR* ドロップを発生させ、先に述べた如く、電気的浮遊領域の電位を決定することになる。

図 9 ガードリング付き Si ダイオード解析電子・正孔分布図 (キャリアリークの発生)

SiC を対象に図 7 の構造に対する計算を実行すると、残念ながら収束解を得ることができない。これは真性キャリア密度の低下に伴い、ダイオード逆方向電流(暗電流)の大きさが急激に低下し、電流値を精度よく求解することが困難となるからである。

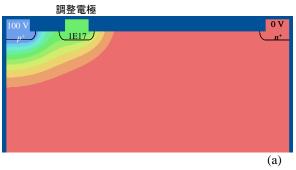

1つの解決策として固定電極を設定し、電流値を 零とする電位を求める問題に変換する処方箋が考 えられる。例えば図 7の構造に対し図 10のような 固定電位問題を設定し、浮遊電位に対応する電極を 調整電極と呼ぶことにする。電気的浮遊状態を実現 するには調整電極端子に流れる電流が零となる電 位を探せばよい。

調整電極を設定することにより求解した浮遊電位を基にガードリング付き SiC ダイオード動作を模擬し、解析した結果を図 11(a)に電位分布図で示す。対照の為、ガードリングを持たない単純 2 次元構造における電位分布を同図(b)に示してある。電位

分布が大きく異なることが見てとれる。

図 10 固定電位電極設定による浮遊電位求解策

調整電極を設定する処方箋は、

- 1) 固定値境界条件問題とすることで数値計算を安定化

- 2) 安定性を得られることから高速計算が可能

- 3) ワイドギャップ半導体でも容易に浮遊電位を決定可能

の利点がある。反面、

- a) 浮遊電位を求解するための反復計算が必要

- b) 浮遊領域が複数になった場合の収束性に課題 が残る。

ワイドギャップ半導体で、且つ浮遊領域を持つ構造解析には数値計算上の技術開発が要求される。

図 11 SiC ダイオード解析。 ガードリングの有無による電位分布の相違。 (a) ガードリング付き、(b) リングなし

#### 4.4. 能動デバイスへの適用例

本節ではハイパワー用能動デバイスの解析・設計 応用について考えていく。

#### 4.4.1. 静電誘導型トランジスタ(SIT)

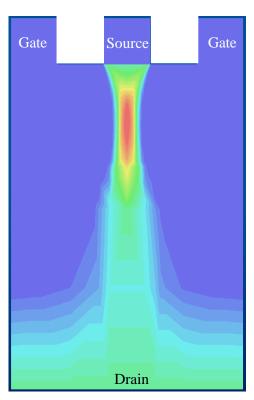

静電誘導型トランジスタ(Static Induction Transistor: SIT) [9] はチャネルを縦構造とし、さらに櫛形配置やメッシュ状配置等により多チャネル高密度実装が可能でハイパワー応用能動素子として有利である。ここでは SiC SIT における単位チャネル当りの動作解析例を図 12 に示す。高いドレイン電圧(300 V)印加によりソース付近の電子がドレイン方向へ誘引(静電誘導)される様子と、縦方向に流れる電流を両サイドのゲートからチャネルを絞り込む動作が電子密度分布図にて示されている。

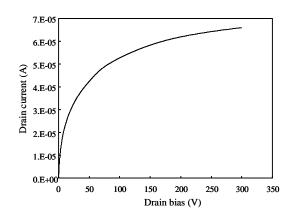

電流一電圧特性にすると、図 13 のようになる。 ゲート・チャネル間は逆バイアスで使用するので、 ゲート電流の大きさ (pn 接合の暗電流)を評価す る必要は通常、起こらない。従ってキャリア密度法 をワイドギャップ半導体の動作解析に使用するこ とは、高電圧解析でも支障が生じない。

図 12 SiC SIT 内部の電子密度分布(300V)

図 13 SiC SIT の電流-電圧特性

#### **4.4.2. GaN HEMT**

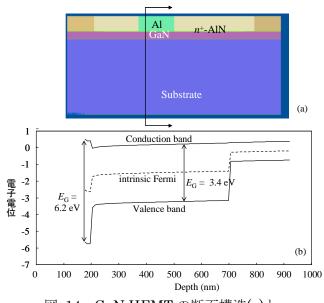

最後に、ワイドギャップ半導体を用いたヘテロ接合デバイスへの適用を調べてみる。 GaN は SiC と同様、3 eV 程度の禁止帯幅をもっている。 GaN 系の特徴は Al を加えたヘテロ構造を利用可能なことである。禁止帯幅は 3-6 eV の大きさに至る。

ここでは HEMT 構造を例にとり解析を進める。 図 14(a)に示すような HEMT 構造に対し、バンド 構造は、同図(b)に示す如く 3 eV と 6 eV の禁止帯 幅をもつ異種材料接触によるヘテロ接合構造となる。大きなバンド不連続を持つ場合、量子効果を電子電位に反映させた有効ポテンシャル法[10]を用いると、キャリア密度法で安定に収束解を得ることができる。

図 14 GaN HEMT の断面構造(a)と バンド構造(b)

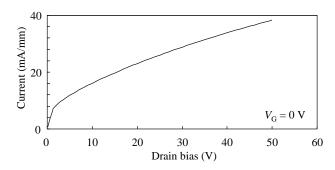

図 15 GaN HEMT 電流-電圧特性

能動層へのキャリア供給としてワイドギャップ側を $n^+$ にドープしたモデルで電流ー電圧特性を計算すると、図 15 の如くなる。50 V まで安定的に計算可能であることも確認される。

4.4.1 ならびに 4.4.2 節の解析例からみると、能動素子に関してはワイドギャップ系に対してもキャリア密度法にて、比較的安定に数値計算可能といえる。

#### 5. おわりに

本稿ではパワーデバイス解析を主題にシミュレーション課題を検討してきた。4.4 節で述べた如く能動素子ではキャリア密度法にて数値計算を比較的安定に行える。ダイオードの逆バイアス特性解析はワイドギャップ系の場合、SRH型再結合電流が著しく小さくなり、計算精度に支障をもたらす。特にガードリングのような浮遊電位問題に大きな影響をもたらす。浮遊電位問題は今後の大きな課題として残る。

#### 参考文献

- [1] M. S. Mock, "A two-dimensional mathematical model of the insulated-gate field-effect transistor", Solid State Electron., vol. 16, pp. 601 609, 1973

- [2] T. Ohtoshi *et. al.*, "A Two-dimensional device simulator of semiconductor lasers", Solid-State Electronics, vol. 30, no. 6, pp. 627 - 638, 1987

- [3] K. Yamaguchi, "A time-dependent and two-dimensional numerical model for

- MOSFET device operation", Solid-State Electronics, vol. 26, no. 9, pp. 907 - 916, 1983

- [4] T. Toyabe, et. al., Three-Dimensional Device Simulator CADDETH with Highly Convergent Matrix Solution Algorithms, IEEE Trans. Computer-Aided Design Int. Circ. Systems, vol. CAD-4, no, 4, pp. 482 – 488, Oct. 1985,

- [5] 倉田 衛、バイポーラトランジスタの動作原理、 近代科学社、昭和 55 年 9 月 20 日初版

- [6] C. Zener, "A theory of the electrical breakdown of solid dielectrics", Proc. Roy. Soc. Vol. 145, pp. 523 – 529, 1934

- [7] E. O. kane, "Theory of tunneling", J. Appl. Phys., vol. 32, no. pp. 83 – 89, 1961

- [8] G. A. M. Hurkx, et. al., "A new recombination model for device simulation including tunneling", IEEE Trans. Electron Devices, vol. 39, no. 2, pp. 331-338, Feb. 1992

- [9] J. Nishizawa, T. Terasaki, and J. Shibata, "Field-effect transistor versus analog transistor (Static Induction Transistor)", IEEE Trans. Electron Devices, vol. ED-22, pp. 185 – 197, April 1975

- [10] 山口 憲、冨澤 一隆, "デバイスシミュレーション · 流体モデルとその発展的応用-", アドバンスシミュレーション, Vol. 5(2010), pp. 64-70